|

|

D5D4D3D2D1 |

D5D4D3D2D1 |

D5D4D3D2D1 |

D5D4D3D2D1 |

D5D4D3D2D1 |

|

D5D4D2D1 |

Ú |

Ú |

|||

|

D5D3D2D1 |

Ú |

Ú |

|||

|

D4D3D2D1 |

Ú |

Ú |

|||

|

D5D4D3D2 |

Ú |

Ú |

![]()

![]()

![]()

![]()

![]() Получаем, что Q5 =

D5D3D2D1ÚD4D3D2D1ÚD5D4D3D2.

Получаем, что Q5 =

D5D3D2D1ÚD4D3D2D1ÚD5D4D3D2.

![]()

![]()

![]()

![]()

![]() В базисе И-НЕ Q5 =

D5D3D2D1× D4D3D2D1× D5D4D3D2.

В базисе И-НЕ Q5 =

D5D3D2D1× D4D3D2D1× D5D4D3D2.

Таблица для Q6

|

|

D5D4D3D2D1 |

D5D4D3D2D1 |

|

D5D4D3D2 |

Ú |

Ú |

![]()

![]()

![]()

Получаем, что Q6 = D5D4D3D2.

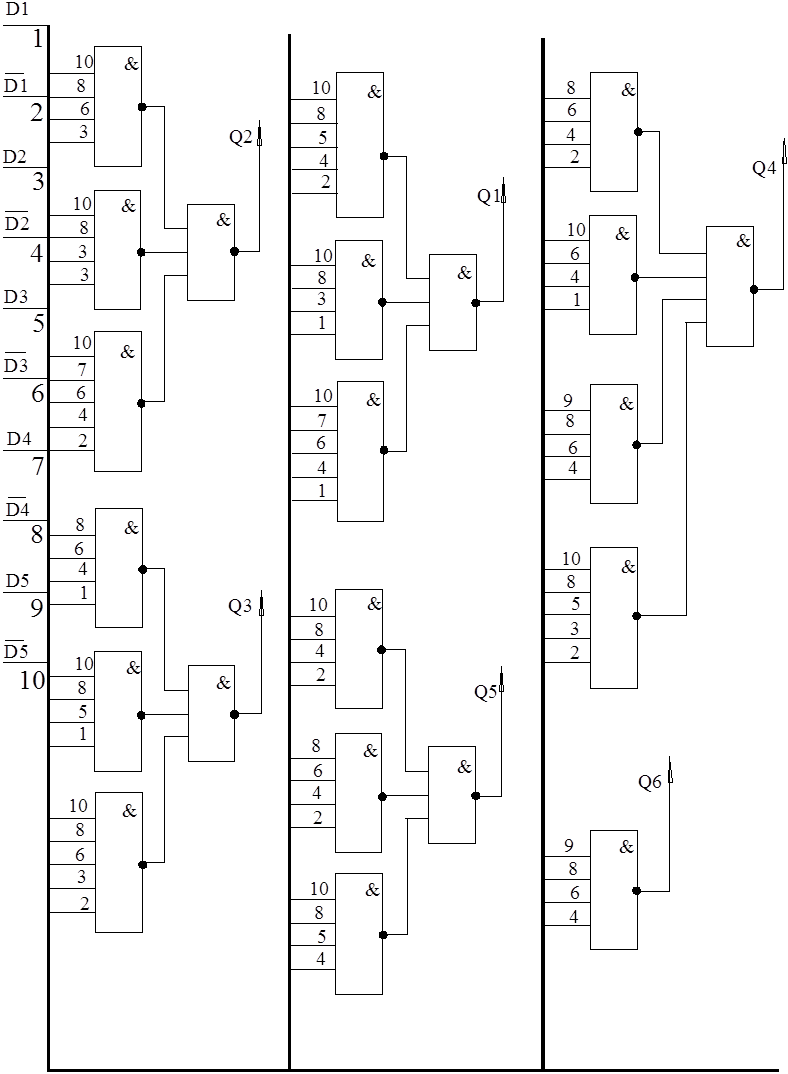

По полученным функциям строим схему преобразователя кодов

(рис.1.4.1).

Диаграмму, поясняющую принцип действия преобразователя кодов, делать необязательно. Так как каждому коду соответствует четко заданная комбинация другого кода.

Рисунок

1.4.1

Преобразователь кодов

1.5. Синтез мультиплексора

Мультиплексор – это коммутационное устройство, с помощью которого осуществляется коммутация передаваемых цифровых сигналов. Мультиплексор имеет информационные входы ( входы дан-

ных). Каждому из информационных входов мультиплексора присваивается адрес, т.е. номер в двоичном коде. При подаче соответствующего двоичного входа, соответствующий информационный вход подключается к выходу.

В нашем случае мультиплексор будет выполнять переход от пар- аллельной формы подачи импульсов в последовательную . В данном мультиплексоре 6 входов данных.

Что бы наглядно увидеть переход от параллельной формы в последовательную составим таблицу истинности, в которой в столбцах

А1 – А3 задаем код для адресных входов, а в столбцах Y1 – Y6 соответственно комбинацию, подаваемую на входы данных.

Таблица истинности мультиплексора

|

А1 |

А2 |

А3 |

Y1 |

Y2 |

Y3 |

Y4 |

Y5 |

Y6 |

|

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

|

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

|

2 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

|

3 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

|

4 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

|

5 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

Cогласно таблице истинности получаем СДНФ для Y1 – Y6.

Y1 = A1A2A3;

![]()

![]() Y2 =

A1A2A3;

Y2 =

A1A2A3;

![]()

![]() Y3 =

A1A2A3;

Y3 =

A1A2A3;

![]() Y4 = A1A2A3;

Y4 = A1A2A3;

![]()

![]() Y5 =

A1A2A3;

Y5 =

A1A2A3;

![]()

![]()

![]() Y6 =

A1A2A3.

Y6 =

A1A2A3.

Для подачи импульсов на адресные входы используем двоичный суммирующий счетчик на D – триггерах с коэффициентом счета 6.

Для построения такого счетчика необходимо три триггера.

Составляем таблицу в которой заполняем предыдущие и последующие состояния, а также сигналы на информационных входах триггеров.

Таблица 1.5.2

Таблица истинности двоичного счетчика

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.