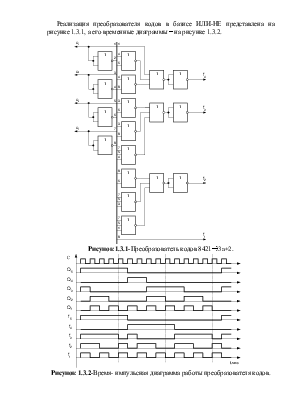

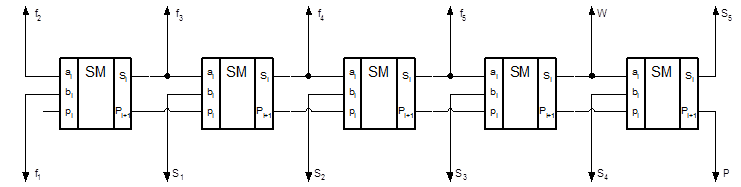

данном курсовом проекте слагаемые на вход сумматора подаются с выходов преобразователя кодов и делителя частоты.

В общем виде функция, реализуемая сумматором имеет вид:

где f1, f2, f3, f4, f5 - сигналы преобразователя кодов,

W - сигналы делителя частоты.

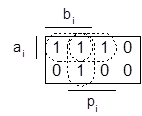

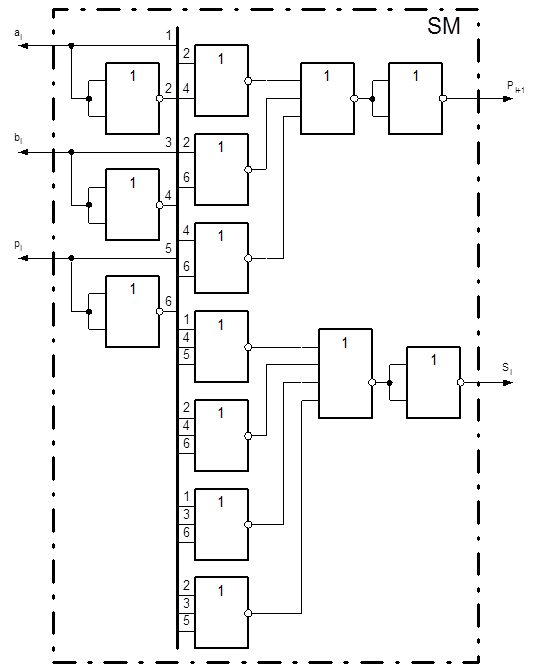

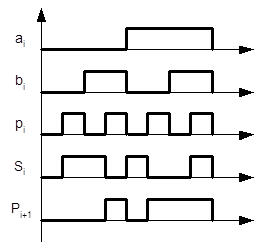

Построим одноразрядный сумматор. Такой сумматор имеет 3 входа для подачи цифр разрядов слагаемых ai, bi и переноса pi. На выходе сумматора формируется сумма Si, и перенос Pi+1, предназначенный для передачи в следующий разряд. Составим таблицу истинности, отображающую работу сумматора.

Таблица 1.5.1. Таблица истинности сумматора.

|

Входы |

Выходы |

|||

|

Слагаемые |

Перенос |

Сумма |

Перенос |

|

|

ai |

bi |

pi |

Si |

Pi+1 |

|

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

1 |

0 |

|

0 |

1 |

0 |

1 |

0 |

|

0 |

1 |

1 |

0 |

1 |

|

1 |

0 |

0 |

1 |

0 |

|

1 |

0 |

1 |

0 |

1 |

|

1 |

1 |

0 |

0 |

1 |

|

1 |

1 |

1 |

1 |

1 |

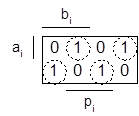

Функции выходов минимизируем методом карт Карно:

Pi+1: Si:

![]()

![]()

Одноразрядный трёхвходовый сумматор с переносом представлен на рис. 1.5.1, общий вид сумматора - на рис. 1.5.2, а его временные диаграммы - на рис. 1.5.3.

|

|

|

1.6. Выбор микросхем

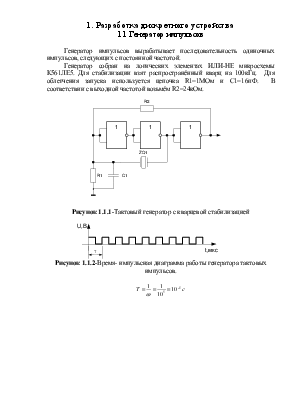

В качестве D-триггера выберем микросхему К561ТМ2. Микросхема K561ТМ2 содержит 2 независимых D-триггера, имеющих общую цепь питания. У каждого триггера имеются D-информационные входы и входы синхронизации С. Триггера также содержат S и R входы для установки в “1” и “0” соответственно. У микросхемы К561ТМ2 вывод 7 – общий, 14 – питание.

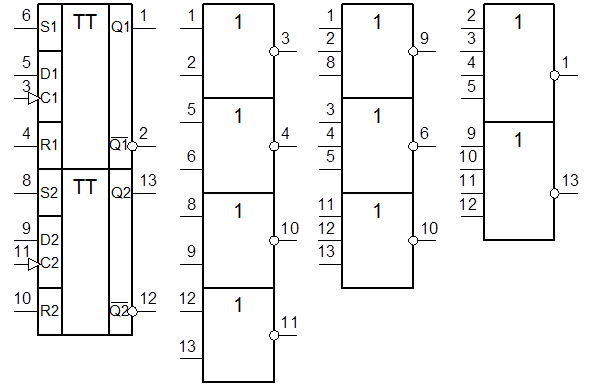

В качестве логических элементов ИЛИ-НЕ будем использовать микросхемы К561ЛЕ5, К561ЛЕ6, К561ЛЕ10. У этих микросхем вывод 7 – общий, 14 – питание. Используемые в дискретном устройстве микросхемы показаны на рис. 1.6.1.

К561ТМ2 К561ЛЕ5 К561ЛЕ10 К561ЛЕ6

Рисунок 1.5.1

|

2 Синтез абстрактного конечного автомата.

Автомат - дискретное устройство, способное принимать различные состояния под воздействием входных сигналов, переходить из одного состояния в другое и вырабатывать выходные сигналы (Л[1] стр. 146).

В данном курсовом проекте требуется синтезировать асинхронный автомат заданный таблицей переходов (таблица 2.1) и таблицей выходов (таблица 2.2).

Таблица переходов. Таблица 2.1

|

|

a1 |

a2 |

|

S0 |

S1 |

S0 |

|

S1 |

S2 |

S1 |

|

S2 |

S0 |

S3 |

|

S3 |

S3 |

S4 |

|

S4 |

S4 |

S2 |

Таблица выходов. Таблица 2.2

|

|

a1 |

a2 |

|

S0 |

1 |

1 |

|

S1 |

1 |

1 |

|

S2 |

0 |

0 |

|

S3 |

0 |

0 |

|

S4 |

0 |

0 |

2.1 Кодирование состояний автомата.

Для синтеза абстрактного асинхронного автомата воспользуемся табличным методом. Для этого прокодируем состояния автомата. Так как состояний автомата 5, будем использовать три JK-триггера. Состояние будет кодироваться тоже тремя битами (таблица 2.3) .

Таблица 2.3

|

S |

Код |

|

A B C |

|

|

S0 |

0 0 1 |

|

S1 |

0 0 0 |

|

S2 |

0 1 0 |

|

S3 |

1 0 0 |

|

S4 |

1 1 0 |

Тогда таблица переходов (таблица 2.4) и таблица выходов (таблица 2.5) закодируются следующим образом.

Таблица переходов. Таблица 2.4

|

|

a1 |

a2 |

|

001 |

000 |

001 |

|

000 |

010 |

000 |

|

010 |

001 |

010 |

|

100 |

100 |

110 |

|

110 |

110 |

010 |

Таблица выходов. Таблица 2.5

|

|

a1 |

a2 |

|

001 |

1 |

1 |

|

000 |

1 |

1 |

|

010 |

0 |

0 |

|

100 |

0 |

0 |

|

110 |

0 |

0 |

2.2 Исключение критических состязаний.

Как видно из таблицы 2.4 критические состязания триггеров B и C происходят при переключении автомата из состояния S2(010) в состояние S0(001) по сигналу a1, и из состояния S4(110) в состояние S2(010) по сигналу a2. Так как автомат по сигналу a2 из состояния S4 дoлжен переходить в состояние S2, затем в состояние S3 и наконец опять в S4, то во время поступления следующего сигнала a1 автомат может находиться, равновероятно, в любом из этих трёх состояний (происходит зацикливание комбинации S4->S2->S3->S4 до поступления сигнала a1). В тоже время сигнал на выходе не будет меняться, а будет всё время равен “0”. Исходя из выше сказанного будем предполагать, что всегда при поступлении сигнала a1 автомат находиться в состоянии S4. Это позволит записать вместо перехода S4 -> S2 переход S4->S4 при котором не происходит критических состязаний в то время как принцип работы автомата не изменится. Аналогично поступим для перехода из состояния S2 в состояние S0 по сигналу a1.

В этом случае таблица переходов (таблица 2.6) запишется следующим образом.

Таблица переходов. Таблица 2.6

|

|

a1 |

a2 |

|

001 |

000 |

001 |

|

000 |

010 |

000 |

|

010 |

011 |

010 |

|

100 |

100 |

110 |

|

110 |

110 |

110 |

2.3 Синтез абстрактного автомата табличным методом.

На основании таблицы переходов и таблицы выходов составим таблицу 2.7, в которой обозначены:

x - значение на входе: a1 - “0”, a2 - “1”.

A, B, C - текущие состояния триггеров.

y - Значение на выходе асинхронного автомата.

A+, B+, C+ - состояния в которые должны переключиться триггеры.

AJ, AK, BJ, BK, CJ, CK - состояния входов триггеров для заданного переключения.

Таблица 2.7

|

x |

A |

B |

C |

A+ |

B+ |

C+ |

Y |

AJ |

AK |

BJ |

BK |

CJ |

CK |

|

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

- |

1 |

- |

0 |

- |

|

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

- |

0 |

- |

- |

1 |

|

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

- |

- |

0 |

0 |

- |

|

0 |

0 |

1 |

1 |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

|

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

- |

0 |

0 |

- |

0 |

- |

|

0 |

1 |

0 |

1 |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

|

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

- |

0 |

- |

0 |

0 |

- |

|

0 |

1 |

1 |

1 |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

- |

0 |

- |

0 |

- |

|

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

- |

0 |

- |

- |

0 |

|

1 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

- |

- |

0 |

0 |

- |

|

1 |

0 |

1 |

1 |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

|

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

- |

0 |

1 |

- |

0 |

- |

|

1 |

1 |

0 |

1 |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

|

1 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

- |

0 |

- |

0 |

0 |

- |

|

1 |

1 |

1 |

1 |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

Таблица переходов JK-Триггера. Таблица 2.8

|

Переход |

J |

K |

|

|

0 |

0 |

0 |

- |

|

0 |

1 |

1 |

- |

|

1 |

0 |

- |

1 |

|

1 |

1 |

- |

0 |

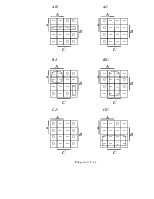

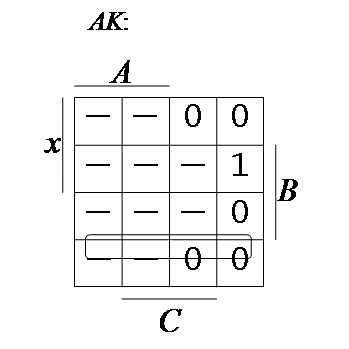

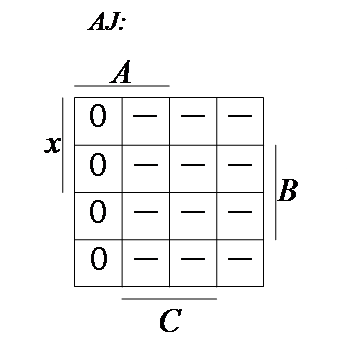

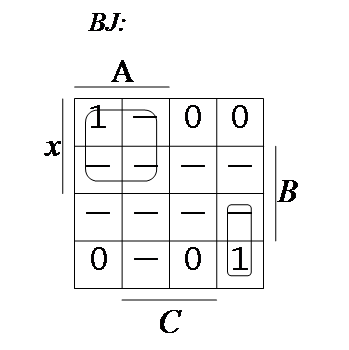

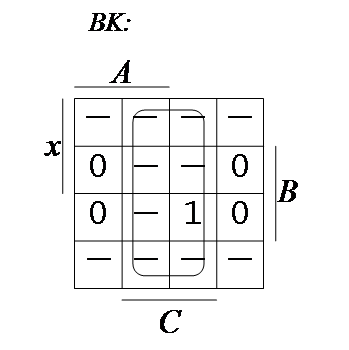

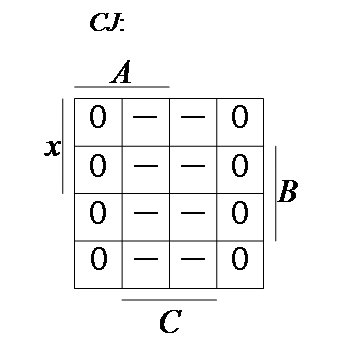

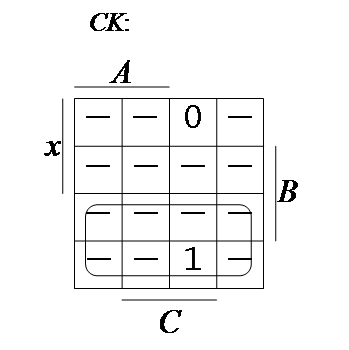

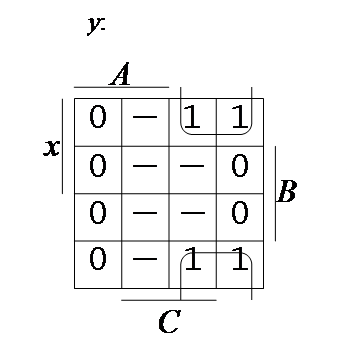

По таблице 2.7 найдём функции, методом карт Карно (рисунок 2.1).

|

|

||||

|

|

||||

|

|

||||

|

|||||

|

||||

|

||||

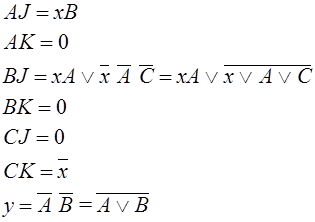

На основании рисунка 2.1 можно составить функции:

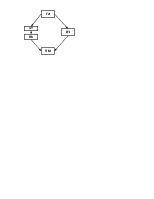

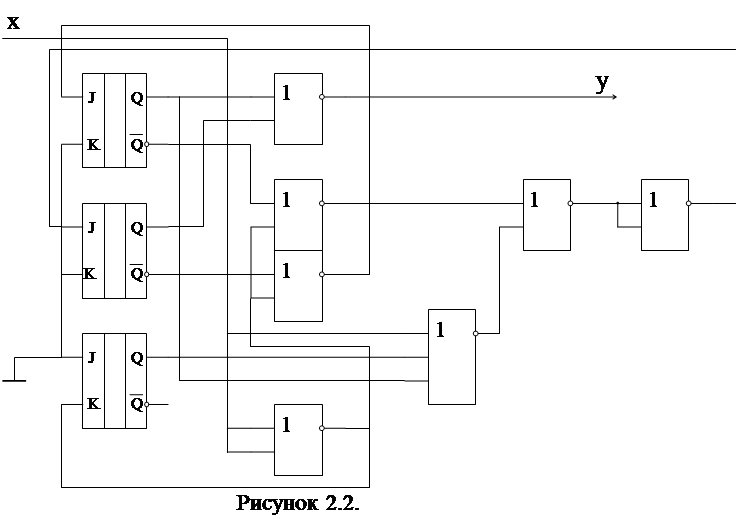

По данным функциям составим электрическую схему (рисунок 2.2).

|

2.2. Выбор микросхем

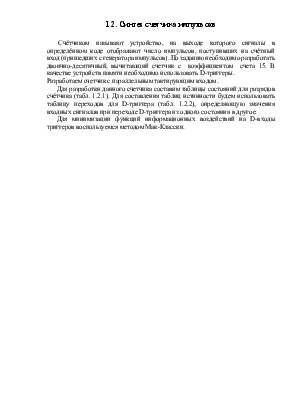

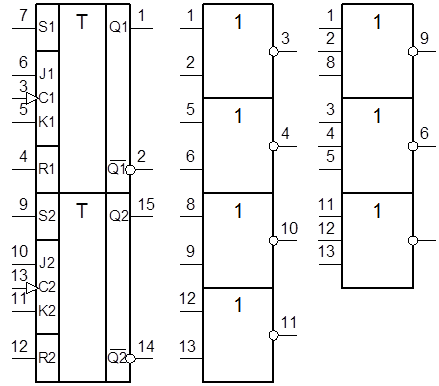

В качестве JK-триггера выберем микросхему К561ТB1. Микросхема K561ТВ1 содержит 2 независимых JK-триггера, имеющих общую цепь питания. У каждого триггера имеются J- и K- информационные входы и входы синхронизации С. Триггера также содержат S и R входы для установки в “1” и “0” соответственно. У микросхемы К561ТВ1 вывод 8 – общий, 16 – питание.

В качестве логических элементов ИЛИ-НЕ будем использовать микросхемы К561ЛЕ5, К561ЛЕ10. У этих микросхем вывод 7 – общий, 14 – питание. Используемые в дискретном устройстве микросхемы показаны на рис. 2.2.1.

|

Рисунок 2.2.1. Разводка микросхем.

Заключение

В результате выполнения курсового проекта была разработана принципиальная схема дискретного устройства (ДУ), имеющего следующую структуру: генератор импульсов, двоично-десятичный вычитающий счетчик с коэффициентом счёта 15, преобразователь кодов (из кода 8421 в код 3a+2), сумматор по модулю два. В качестве элементов памяти использовал D–триггеры. Дискретное устройство реализовано в базисе ИЛИ - НЕ.

Кроме того был синтезирован асинхронный автомат по таблицам

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.