1.5 Синтез мультиплексора

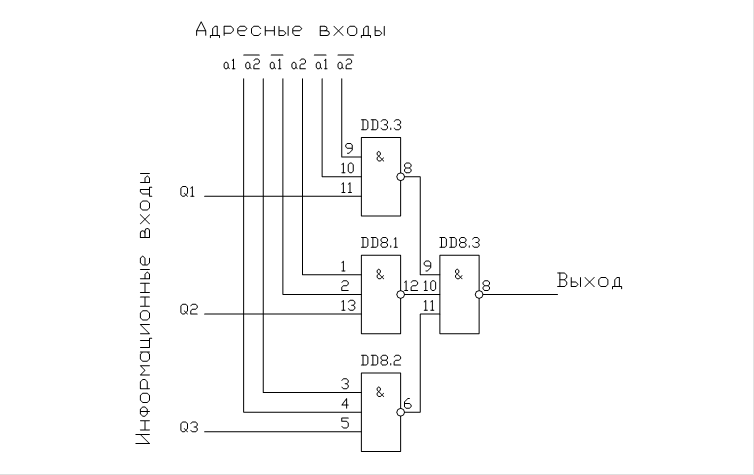

Мультиплексор в данной схеме служит для преобразования выходного кода счетчика в параллельном виде в последовательную форму. Это происходит путем последовательного опроса выходов счетчика, подключенных к информационным входам мультиплексора. К адресным входам подключены выходы делителя частоты, позволяющие последовательно адресовать все три основных (неинвертированных) выхода счетчика.

Для преобразования трехразрядного двоичного кода в последовательную форму нам понадобится мультиплексор с тремя информационными и двумя адресными входами, т. к. с помощью одного адресного входа можно адресовать только две информационных линии.

Таким образом, функция алгебры логики, описывающая работу требуемого устройства может быть записана в следующем виде:

Следует также обратить внимание на то, что на выходе мультиплексора первым будет следовать сигнал, отвечающий за состояние старшего разряда счетчика.

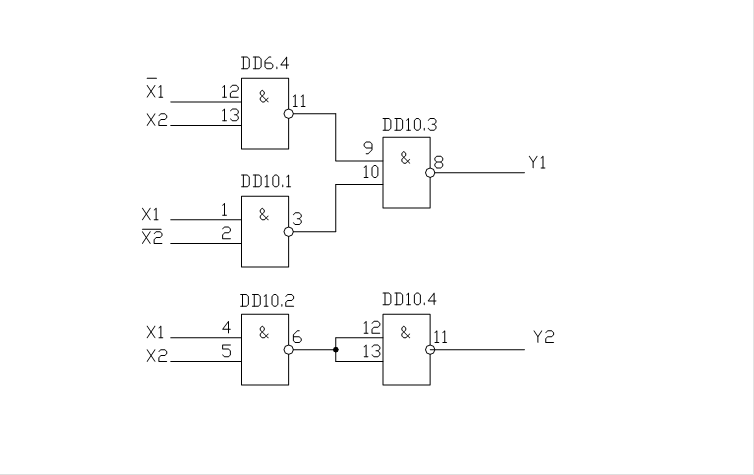

Для схемной реализации выберем микросхему К155ЛА4, содержащую три трехвходовых элемента И-НЕ. Данную микросхему мы использовали ранее, поэтому нет необходимости повторять ее описание. Принципиальная схема мультиплексора изображена на рис. 1.13.

|

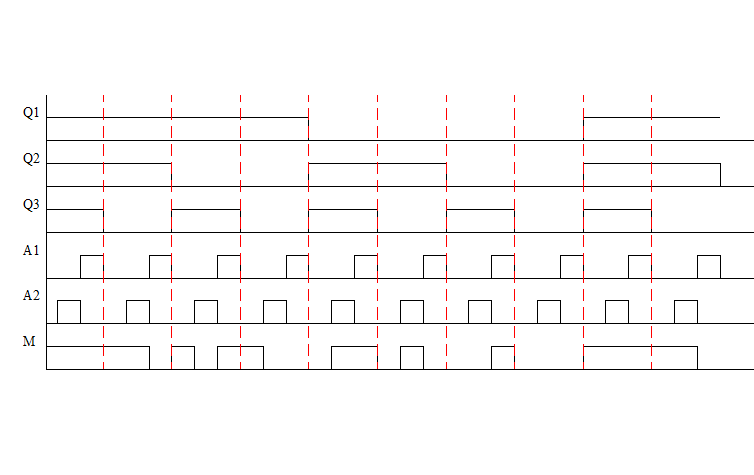

Поясним работу мультиплексора с помощью временных диаграмм (рис.1.14).

Рис. 1.14. Временные диаграммы работы мультиплексора

Рассмотрим первый цикл работы мультиплексора. На информационные входы мультиплексора поступают сигналы низкого уровня с выходов Q1, Q2, Q3 счетчика. В момент, когда на адресных входах будут установлены сигналы логической единицы, на выходе мультиплексора появится сигнал с первого информационного входа, т. е. Q1. Затем на адресных входах будет установлена комбинация 01 (A1=0, A2=1), на выходе мультиплексора появится сигнал со второго информационного входа, т. е. с Q2. Если на адресных входах будут высокие уровни, то на выходе мультиплексора будет присутствовать сигнал Q3. В схеме данного проекта на адресные входы подаются уровни, снимаемые с выходов счетчика-делителя. Благодаря этому происходит преобразование кода из параллельной формы в последовательную.

1.6 Синтез сумматора по модулю два

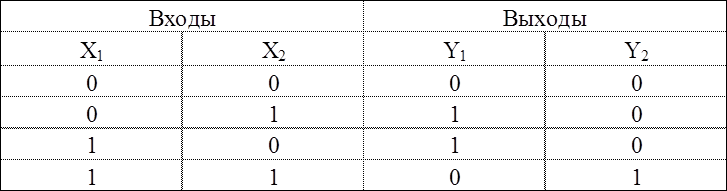

Сумматор по заданной структуре должен суммировать последовательный код, поступающий на один из его входов, и сигналы, поступающие на его второй вход с делителя частоты.

Обозначим входы сумматора X1 и X2, а выходы Y1 и Y2. Составим таблицу истинности сумматора (табл. 1.6). напряжение высокого уровня на его выходе Y1 должно появляться только в том случае, когда на одном из его входов присутствует логическая единица, а на втором – нуль. В других случаях на данной линии должен присутствовать потенциал, соответствующий низкому уровню. Единичный сигнал на линии Y2 должен появляться только, если на обоих входах сумматора присутствует сигнал высокого уровня. Вышеизложенное отражено в табл. 1.6.

|

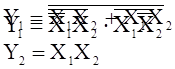

Из таблицы истинности, даже не совершая попытку минимизации, видно, что функции Y1 и Y2 не могут быть минимизированы. Таким образом, можно сразу записать СДНФ для этих функций.

|

Для реализации сумматора в виде схемы нам понадобится три двухвходовых элемента И-НЕ и один элемент И.

Для схемной реализации воспользуемся уже использованными ранее микросхемами К155ЛА3. Принципиальная схема приведена на рис. 1.14.

На выходе сумматора Y1 будет появляться логическая единица, если на одном из входов будет присутствовать сигнал высокого уровня, в остальных случаях на данном выходе будет появляться низкий потенциал. Логическая единица на выходе Y2 появится тогда и только тогда, когда на обоих входах сумматора будет присутствовать высокое напряжение.

|

1.7 Устройство управления

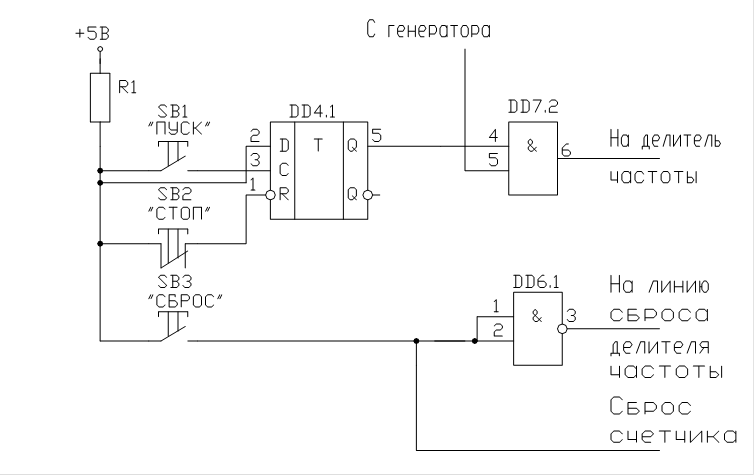

Устройство управления (рис. 1.15) в данной схеме предназначено для управления работой схемы. Оно включает в себя схему, обеспечивающую пуск и останов счета, а также схему, обеспечивающую сброс счетчика в начальное состояние.

Для того, чтобы схема дискретного устройства начала работу, необходимо нажать на кнопку ПУСК. При нажатии данной кнопки на вход синхронизации триггера DD4.1 К155ТМ2 поступит положительный перепад напряжения, по которому постоянно присутствующее на входе данных D триггера напряжение высокого уровня поступит на его выход, открывая тем самым временной селектор DD7.2 К155ЛИ1. Таким образом, на вход делителя частоты начнут поступать импульсы с генератора.

При нажатии кнопки СТОП произойдет сброс триггера, в результате чего низкий уровень сигнала на управляющем входе временного селектора закроет канал прохождения тактовых импульсов, т. е. произойдет прекращение счета. Для возобновления работы схемы необходимо нажать кнопку ПУСК. Сброс счетчика при этом не произойдет.

Для сброса содержимого счетчика в схеме управления предусмотрена кнопка СБРОС, при нажатии которой по линии сброса счетчика на D-входах всех триггеров установится высокий уровень, который с приходом следующего тактового импульса будет записан в триггеры. При нажатии данной кнопки произойдет также обнуление триггеров делителя частоты, т. к. на инверсные входы сброса их через инвертор DD6.1 поступит сигнал логического нуля, по которому триггеры перейдут в нулевое состояние.

Рис. 1.15. Принципиальная схема устройства управления

|

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.