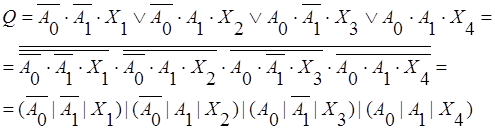

Составим функцию для выхода мультиплексора.

![]()

Переведем эту функцию в базис И-НЕ и представим ее при помощи штрихов Шеффера.

Схема мультиплексора представлена на рисунке 1.6.Временная диаграмма представлена на рисунке 1.9.

Дискретное устройство, разрабатываемое в курсовом проекте, состоит из генератора прямоугольных импульсов, счетчика, дешифратора, шифратора и мультиплексора.

Генератор вырабатывает последовательность прямоугольных импульсов с частотой 100 кГц, которая подается на триггеры счетчика.

Счетчик осуществляет счет количества импульсов поступивших на его вход с генератора и представляет их количество в двоичном коде. Коэффициент счета равен 9, поэтому при приходе 9-го импульса счетчик обнуляется, и счет возобновляется сначала.

Дешифратор представляет двоичный код, приходящий со счетчика в десятичный код посредством вырабатывания высокого импульса на одном из выходов.

Шифратор преобразует десятичный код, пришедший с дешифратора, в двоичный код.

На мультиплексор, в качестве адресных, поступают два младших разряда счетчика. По состояниям на адресных входах мультиплексор подключает к своему выходу один из информационных входов, в качестве которых служат выходы шифратора.

Временная диаграмма работы дискретного устройства приведена на рисунке 1.9

Принципиальная схема дискретного устройства приводится в приложении 1. Спецификация приведена в приложении 2.

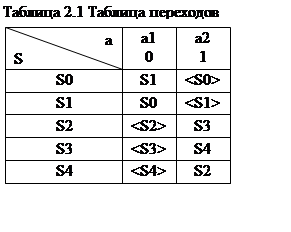

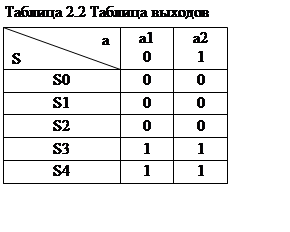

По заданию необходимо построить асинхронный автомат на D триггерах по таблицам переходов (таблица 2.1) и выходов (таблица 2.2).

Автомат - дискретное устройство, способное принимать различные состояния под воздействием входных сигналов, переходить из одного состояния в другое и вырабатывать выходные сигналы.

|

|

||||||

|

|||||||

|

|||||||

При переходе из S4 в S2 возникает критическое состязание. Для того чтобы избавиться от него введем задержку.

Таблицы примут вид после введения задержки.

Таблица 2.4 Таблица переходов

|

S\a |

a1 |

a2 |

|

S0 |

S1 |

<S0> |

|

S1 |

S0 |

<S1> |

|

S2 |

<S2> |

S3 |

|

S3 |

<S3> |

S4 |

|

S4 |

<S4> |

S5 |

|

S5 |

<S5> |

S2 |

Таблица 2.5 Таблица выходов

|

S\a |

1 |

0 |

|

S0 |

0 |

0 |

|

S1 |

0 |

0 |

|

S2 |

0 |

0 |

|

S3 |

1 |

1 |

|

S4 |

1 |

1 |

|

S5 |

1 |

1 |

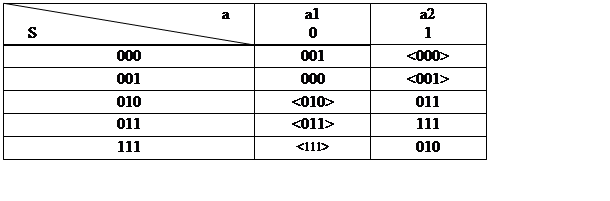

Таблица 2.6 Кодирование состояний системы

|

S\a |

a1 |

a2 |

|

000 |

001 |

<000> |

|

001 |

000 |

<001> |

|

010 |

<010> |

011 |

|

011 |

<011> |

111 |

|

111 |

<111> |

110 |

|

110 |

<110> |

010 |

Сведем все таблицы к одной.

Таблица 2.7 Обобщенная таблица

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.