|

Входные воздействия |

Предыдущие состояния триггеров |

Последующие состояния триггеров |

Информационные воздействия на входы триггеров |

|||||||||||

|

X(t) |

Y1(t-1) |

Y2(t-1) |

Y3(t-1) |

Y1(t) |

Y2(t) |

Y3(t) |

J1 |

K1 |

J2 |

K2 |

J3 |

K3 |

||

|

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

~ |

0 |

~ |

0 |

~ |

||

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

~ |

0 |

~ |

0 |

~ |

||

|

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

~ |

0 |

~ |

~ |

0 |

||

|

1 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

~ |

1 |

~ |

~ |

1 |

||

|

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

~ |

~ |

0 |

0 |

~ |

||

|

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

~ |

~ |

0 |

1 |

~ |

||

|

0 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

~ |

~ |

0 |

~ |

0 |

||

|

1 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

~ |

~

|

1 |

~ |

0 |

||

|

0 |

1 |

0 |

0 |

0 |

0 |

0 |

~ |

1 |

0 |

~ |

0 |

~ |

||

|

1 |

1 |

0 |

0 |

1 |

0 |

0 |

~ |

0 |

0 |

~ |

0 |

~ |

||

|

![]()

|

|

||||

|

|||||

![]()

![]()

![]()

![]()

|

||||

|

||||

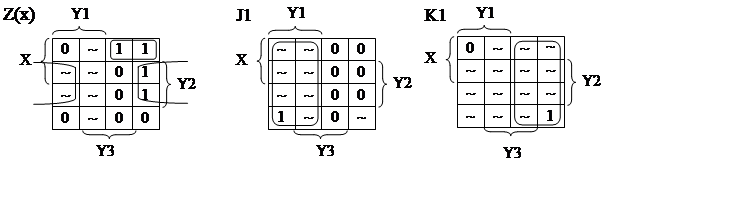

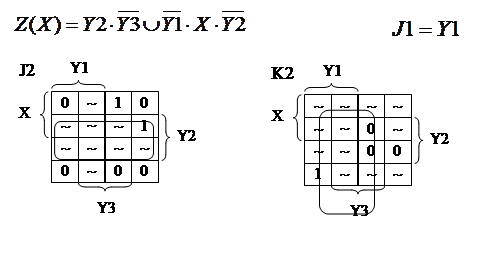

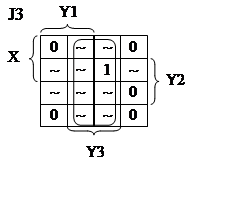

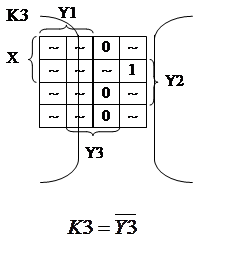

Делитель частоты - это устройство, которое при подаче на его вход периодической импульсной последовательности формирует на выходе такую же импульсную последовательность, но имеющую частоту повторения импульсов в заданное число раз меньшую, чем во входной последовательности. Для того, чтобы в мультиплексоре преобразовать параллельный код в последовательный, необходимо, чтобы информация на адресных входах мультиплексора изменялась в пять раз быстрее чем на информационных. Для этого перед двоично-десятичным счетчиком синтезируем делитель частоты с коэффициентом пять. В качестве делителя частоты используем четыре JK -триггера. Делитель строим по принципу построения счётчика. Одновременно данный делитель будем использовать в качестве двоичного счётчика с коэффициентом счёта ксч=6 для подачи на адресные входы мультиплексора.

Определим число триггеров путём перевода ксч, заданного в десятичной форме в двоичную систему счисления:

2к-1![]() 6

6![]() 2к

2к

Отсюда, к=3, т.е. необходимо три триггера;

Составим таблицу 1.3.1 предыдущего и последующего состояния счётчика, где расписываем все состояния входов:

Таблица 1.3.1

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.