Мультиплексор осуществляет преобразование из параллельной формы представления числа в последовательную.

Дискретное устройство реализовано в базисе «И-ИЛИ-НЕ».

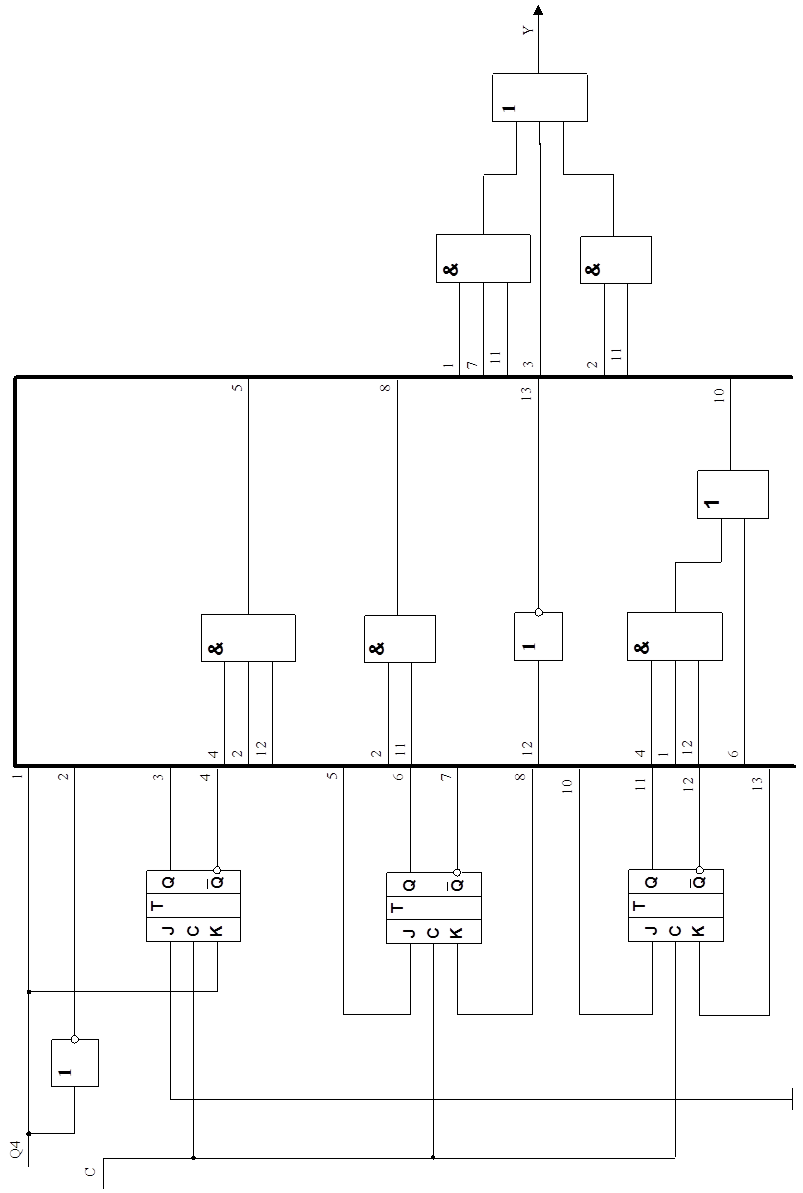

Электрическая принципиальная схема дискретного устройства приводится в приложении 1. Спецификация приведена в приложении 2.

1.7 Выбор микросхем

Элементная база дискретного устройства основана на 555 ТТЛШ серии. Это обусловлено её дешевизной и доступностью.

Параметры 555 ТТЛ серии

Кратковременное (в течение не более 5 мс) максимальное напряжения питания 7 В.

Максимальное напряжение источника питания 6 В.

Диапазон рабочих температур -45..+70oC.

Напряжение источника питания +5 В.

В качестве логических элементов И, ИЛИ, НЕ, ИЛИ-НЕ будем использовать микросхемы К555ЛИ1, К555ЛЛ1, К555ЛИ3, К555ЛИ6, К555ЛЛ7, К555ЛИ4, К555ЛЕ1, у которых вывод 7- общий, 14- питание. На выводы 14 этих микросхем подаётся +5 В, а на выводы 7 подаётся 0 В.

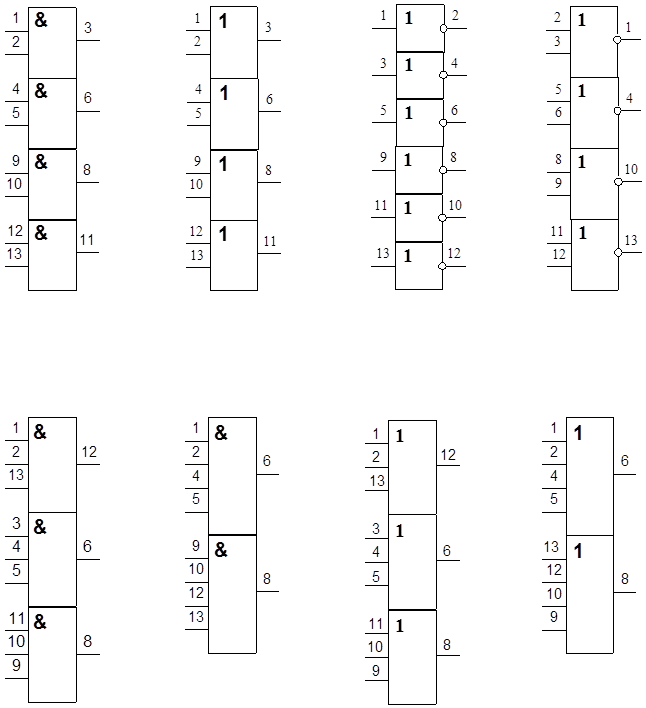

Нумерация выводов показана на рисунке 13.

К555ЛИ1 К555ЛИ1 К555ЛН2 К555ЛЕ1

К555ЛИ3 К555ЛИ6 К555ЛИ4 К555ЛЛ7

Рисунок 13 - Микросхемы серии К555

В качестве JK - триггера выберем микросхему К155ТB15. Серии К155 и К555 совместимы по входам и выходам.

Микросхема K155ТВ15 содержит 2 независимых комбинированных JK-триггера, имеющих общую цепь питания. У каждого триггера имеются J- и К- информационные входы и входы синхронизации С. Триггера также содержат S и R входы для установки в «1» и «0» соответственно. У микросхемы К155ТВ15 вывод 8 – общий, 16 – питание. На вывод 8 подаётся 0, а на вывод 16 подаётся +5 В.

2 Синтез абстрактного автомата

2.1 Разработка асинхронного автомата

Автоматом называется дискретное устройство, способное принимать различные состояния, под воздействием входных сигналов переходить из одного состояния в другое и вырабатывать выходные сигналы.

Математической моделью дискретного устройства, обладающего памятью, является абстрактный автомат, который задается совокупностью пяти конечных множеств:

S = {A, Z, W, d, x}, где А = {а0,а1 ... аМ} - множество состоянии автомата, причем а0 - начальное состояние;

Z = {Z1,Z2 ... Zf} - множество входных сигналов;

W = {W1,W2 ... WС} - множество выходных сигналов;

d - функция переходов, обеспечивающая выработку последующего м состояния aS автомата в зависимости от существующего состояния аM и входного воздействию Zf ;

x - функция выходов, обеспечивающая выработку выходного сигнала автомата в зависимости от его состояния и входного сигнала Zf.

Абстрактный автомат имеет один входной и один выходной каналы, и каждой букве входного алфавита Z ставит в соответствие букву или слово выходного алфавита W.

Наибольшее распространение получили автоматы Мили и Мура.

Закон функционирования автомата Мили:

a( t + 1) = d( a( t ) ; Z( t )) ;

W( t ) = x ( a( t ) ; Z( t ) ) .

Работу автомата Мура определяется следующими уравнениями:

a( t + 1 ) = d((a(t),Z(t));

W( t ) = x ( a( t ) ), где t = 0,1,2...

Автомат может задаваться несколькими способами, однако все они должны конкретизировать функции переходов и выходов. Задание автомата табличным способом заключается в построении таблиц переходов ТП и выходов ТВ, в которых показываются внутренние состояние и состояния выходов автомата в соответствии с функциями переходов и выходов. Графическое представление автомата осуществляется с помощью графа, вершины которого соответствуют внутренним состояниям автомата. Переходы из одного состояния в другое показывают стрелками, соответствующими ветвям графа.

В данном курсовом проекте требуется синтезировать табличным методом асинхронный автомат, заданный таблицей переходов (таблица 11) и таблицей выходов (таблица 12).

Таблица 11 - Таблица переходов

|

|

a1 |

a2 |

|

S0 |

S3 |

<S0> |

|

S1 |

<S1> |

S2 |

|

S2 |

S4 |

S3 |

|

S3 |

<S3> |

S2 |

|

S4 |

S0 |

<S4> |

Таблица 12 - Таблица выходов

|

|

a1 |

a2 |

|

S0 |

0 |

0 |

|

S1 |

1 |

1 |

|

S2 |

1 |

0 |

|

S3 |

0 |

0 |

|

S4 |

1 |

1 |

Произведём кодировку состояний автомата. Так как состояний автомата 5, будем использовать три JK-триггера. Состояние будет кодироваться тремя битами (таблица 13) .

|

S |

Код |

|

A B C |

|

|

S0 |

0 1 1 |

|

S1 |

1 0 0 |

|

S2 |

0 0 0 |

|

S3 |

0 0 1 |

|

S4 |

0 1 0 |

Тогда таблица переходов (таблица 14) и таблица выходов (таблица 15) будет выглядеть следующим образом.

Таблица 14 - Таблица переходов.

|

|

a1 |

a2 |

|

011 |

001 |

<011> |

|

100 |

<100> |

000 |

|

000 |

010 |

001 |

|

001 |

<001> |

000 |

|

010 |

011 |

<010> |

Таблица 15 - Таблица выходов.

|

|

a1 |

a2 |

|

011 |

0 |

0 |

|

100 |

1 |

1 |

|

000 |

1 |

0 |

|

001 |

0 |

0 |

|

010 |

1 |

1 |

На основании таблицы переходов и таблицы выходов составим таблицу 16, в которой обозначены:

x - значение на входе: a1 - “0”, a2 - “1”.

A, B, C - текущие состояния триггеров.

y - Значение на выходе асинхронного автомата.

A+, B+, C+ - состояния в которые должны переключиться триггеры.

AJ, AK, BJ, BK, CJ, CK - состояния входов триггеров для заданного переключения.

Таблица 16

|

x |

A |

B |

C |

A+ |

B+ |

C+ |

Y |

AJ |

AK |

BJ |

BK |

CJ |

CK |

|

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

~ |

~ |

1 |

~ |

0 |

|

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

~ |

0 |

0 |

~ |

0 |

~ |

|

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

~ |

1 |

~ |

0 |

~ |

|

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

~ |

0 |

~ |

~ |

0 |

|

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

~ |

~ |

0 |

1 |

~ |

|

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

~ |

~ |

0 |

~ |

0 |

|

1 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

~ |

1 |

0 |

~ |

0 |

~ |

|

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

~ |

0 |

~ |

1 |

~ |

|

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

~ |

0 |

~ |

~ |

1 |

|

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

~ |

~ |

0 |

0 |

~ |

Таблица 17 - Таблица переходов JK-Триггера

|

Переход |

J |

K |

|

|

0 |

0 |

0 |

~ |

|

0 |

1 |

1 |

~ |

|

1 |

0 |

~ |

1 |

|

1 |

1 |

~ |

0 |

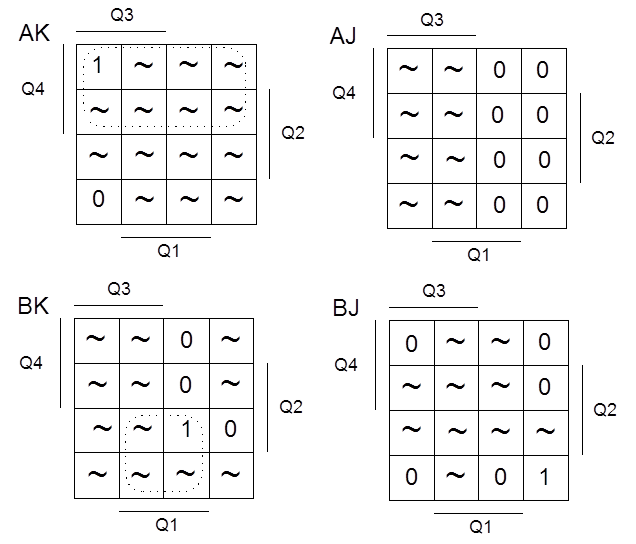

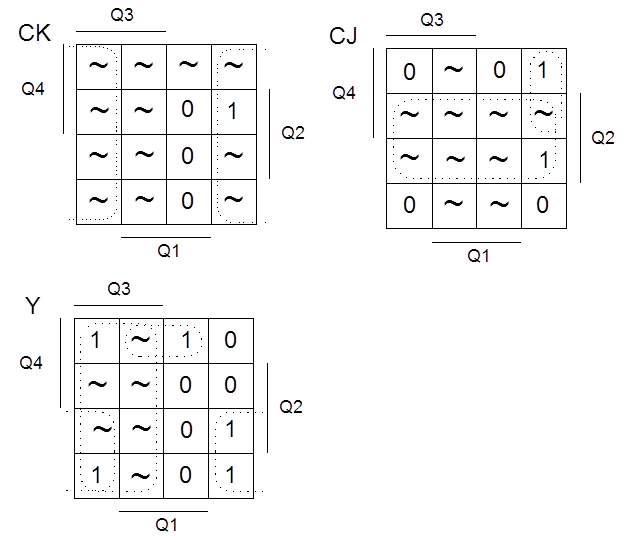

По таблице 16 найдём функции, методом карт Карно (рисунок 14).

|

Рисунок 14 - Карты Карно

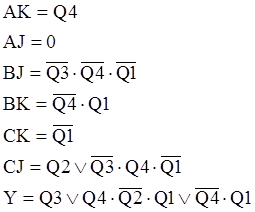

По картам Карно составим функции:

По данным функциям составим электрическую схему (рисунок 15).

![]()

Заключение

В курсовом проекте было разработано дискретное устройство и синтезирован абстрактный конечный автомат. А так же получены навыки разработки цифровых устройств, таких как счётчики, делители частоты, мультиплексоры, преобразователи. Изучена методика минимизации функций алгебры-логики. Освоены принципы построения надёжных схем и способы исключения критических состязаний. Изучены обозначения ГОСТ для электрических принципиальных схем

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.