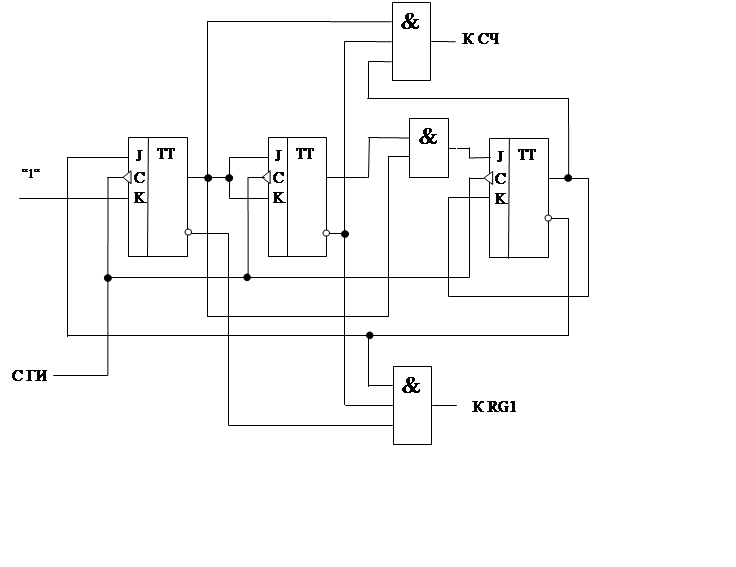

Элементы 3И в схеме делителя частоты необходимы для обеспечения необходимой длительности импульсов.

|

Рисунок 1.3.7. Делитель частоты с N=6

1.4. СЧЕТЧИК

Требуется построить суммирующий двоично-десятичный счетчик на JK триггерах с коэффициентом счета равным тринадцать.

Двоично-десятичный счётчик строится по поразрядному принципу. Каждый разряд десятичного числа представляет собой двоичный счётчик и затем с помощью специальных схемных решений эти двоичные счётчики соединяются между собой.

Выберем двоичный счетчик с параллельным переносом. Счетчики с параллельным переносом имеют более высокое быстродействие. Это связано с тем, что в таких счетчиках входной сигнал непосредственно воздействует на синхронизирующий вход каждого триггера, в то время как на другие входы подаются управляющие сигналы от предшествующих триггеров [ ].

Определим число триггеров путём перевода Ксч, заданного в десятичной форме в двоичную систему счисления:

2к-1![]() 9

9![]() 2к;

2к;

Отсюда, К=4, т.е. на младший разряд необходимо четыре триггера, а на старший один триггер.

Изменение состояний триггеров и управляющие воздействия на их входах приведем в таблице 1.4.

Таблица 1.4

ТИ счетчика

|

Номер входного импульса |

Предыдущее состояние |

Последующее Состояние |

Сигналы на информационных входах триггеров |

|||||||||||||

|

Q4n |

Q3n |

Q2n |

Q1n |

Q4n+1 |

Q3n+1 |

Q2n+1 |

Q1n+1 |

J4 |

K4 |

J3 |

K3 |

J2 |

K2 |

J1 |

K1 |

|

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

~ |

0 |

~ |

0 |

~ |

1 |

~ |

|

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

~ |

0 |

~ |

1 |

~ |

~ |

1 |

|

2 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

~ |

0 |

~ |

~ |

0 |

1 |

~ |

|

3 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

~ |

1 |

~ |

~ |

1 |

~ |

1 |

|

4 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

~ |

~ |

0 |

0 |

~ |

1 |

~ |

|

5 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

~ |

~ |

0 |

1 |

~ |

~ |

1 |

|

6 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

~ |

~ |

0 |

~ |

0 |

1 |

~ |

|

7 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

~ |

~ |

1 |

~ |

1 |

~ |

1 |

|

8 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

~ |

0 |

0 |

~ |

0 |

~ |

1 |

~ |

|

9 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

~ |

1 |

0 |

~ |

0 |

~ |

~ |

1 |

Согласно таблице 1.4 запишем СДНФ функций возбуждения триггеров.

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

Минимизируем функции возбуждения входов триггеров с помощью метода карт Карно.

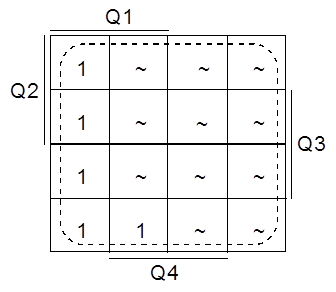

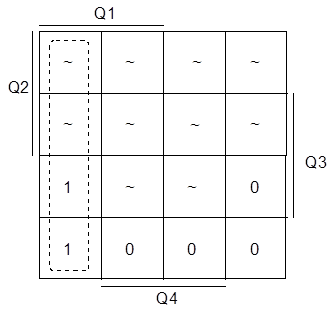

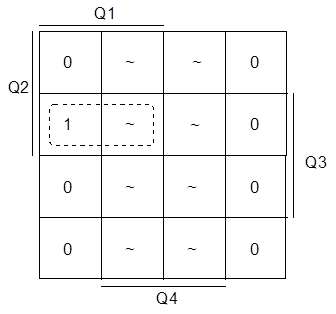

Для K1 имеем карту Карно, представленную на рисунке1.4.1.

|

Рисунок 1.4.1. Карта Карно для К1

![]()

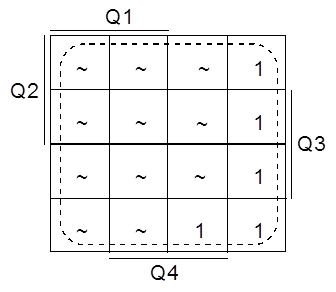

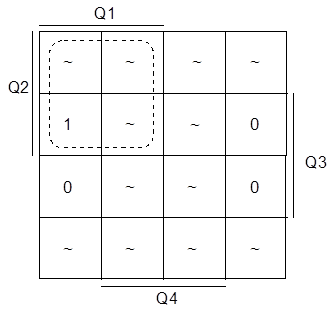

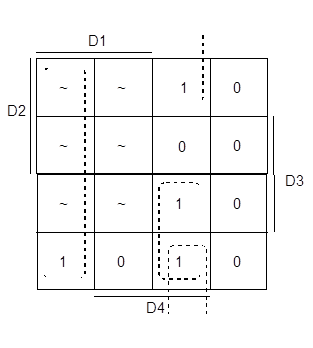

Для J1 имеем карту Карно, представленную на рисунке1.4.2.

|

Рисунок 1.4.2. Карта Карно для J1

![]()

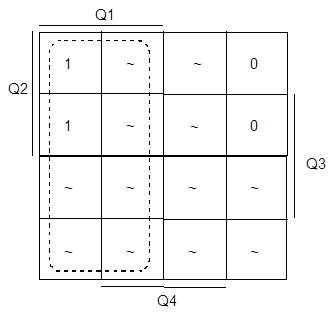

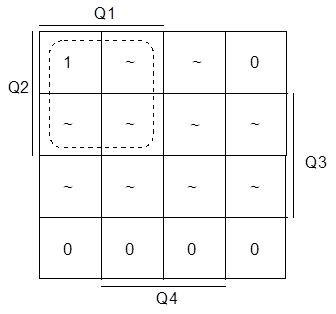

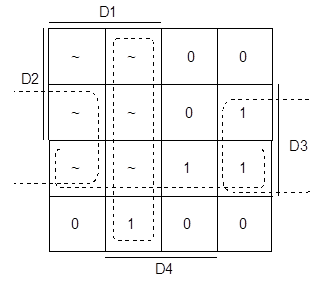

Для K2 имеем карту Карно, представленную на рисунке1.4.3.

|

Рисунок 1.4.3. Карта Карно для K2

![]()

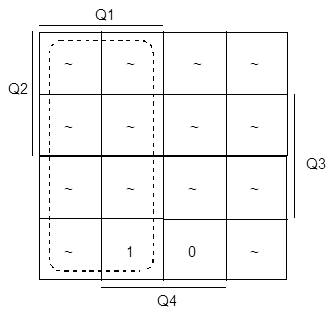

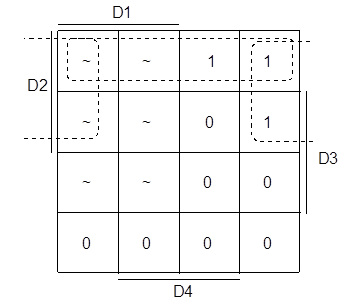

Для J2 имеем карту Карно, представленную на рисунке1.4.4.

|

Рисунок 1.4.4. Карта Карно для J2

![]()

Для K3 имеем карту Карно, представленную на рисунке1.4.5.

|

Рисунок 1.4.5. Карта Карно для K3

![]()

Для J3 имеем карту Карно, представленную на рисунке1.4.6.

|

Рисунок 1.4.6. Карта Карно для J3

![]()

Для K4 имеем карту Карно, представленную на рисунке1.4.7.

|

Рисунок 1.4.7. Карта Карно для K4

![]()

Для J4 имеем карту Карно, представленную на рисунке1.4.8.

|

Рисунок 1.4.8. Карта Карно для J4

![]()

Для функционирования счетчика необходима схема, которая бы работала следующим образом: когда счетчик десятков установлен в ноль, то счетчик единиц считает до десяти, а когда счетчик десятков установлен в единицу – счетчик единиц считает до трех, и кроме того, при поступлении четырнадцатого импульса необходимо установить все триггера счетчика в нулевое состояние.

Счетчик десятков будет устанавливаться в единицу при нуле на каждом неинверсном выходе счетчика единиц. Для этого необходимо использовать логический элемент 4И, на вход которого подаются инверсные сигналы со всех выходов счетчика единиц.

Для установки всех триггеров счетчика в

нулевое состояние при поступлении четырнадцатого импульса необходимо

использовать логический элемент 5И, на вход которого подаются сигналы ![]() . На выходе элемента 5И необходимо

поставить инвертор, так как используемые нами триггеры имеют инверсный вход

установки в ноль.

. На выходе элемента 5И необходимо

поставить инвертор, так как используемые нами триггеры имеют инверсный вход

установки в ноль.

Схема двоично-десятичного счётчика с коэффициентом счёта Ксч= 13 приведена на рисунке 1.4.9.

1.5. ПРЕОБРАЗОВАТЕЛЬ КОДОВ

Преобразователи используются для повышения помехоустойчивости процесса передачи информации. Двоичные сигналы с помощью преобразователя кодируют, то есть придают некоторый признак, по которому на приемной стороне можно сказать, произошла или не произошла ошибка при передачи сообщения [ ].

Необходимо построить преобразователь из кода 8421 в код 7421 .

Преобразователь строится отдельно для каждого разряда двоично-десятичного счетчика, но так как в нашем случае счетчик имеет коэффициент счета равный тринадцати, то для счетчика десятков нет необходимости строить преобразователь кодов. Это обусловлено тем, что число 0 и 1 в коде 8421 и в коде 7421 не отличаются.

Код 7421 представляет интерес тем, что в нем любая кодовая комбинация содержит не более двух единиц.

Функционирование преобразователя кодов задано таблице 1.5.

Таблица 1.5

ТИ преобразователя кодов

|

Десятичное |

Входы преобразователя (код 8421) |

Выходы преобразователя код (7421) |

||||||

|

D4 |

D3 |

D2 |

D1 |

Q4 |

Q3 |

Q2 |

Q1 |

|

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

|

2 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

|

3 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

|

4 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

|

5 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

|

6 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

|

7 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

|

8 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

|

9 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

Запишем СДНФ для выходов преобразователя Q1, Q2, Q3, Q4.

![]()

![]()

![]()

![]()

Минимизируем функции выходов преобразователя кодов с помощью карт Карно.

Для Q1 имеем карту Карно, представленную на рисунке 1.5.1.

|

Рисунок 1.5.1. Карта Карно для Q1

![]()

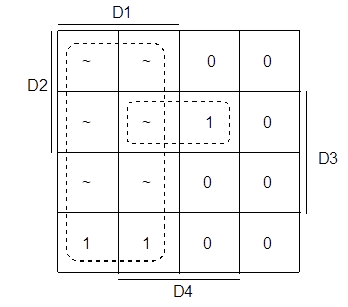

Для Q2 имеем карту Карно, представленную на рисунке 1.5.2.

|

Рисунок 1.5.2. Карта Карно для Q2

![]()

Для Q3 имеем карту Карно, представленную на рисунке 1.5.3.

|

Рисунок 1.5.3. Карта Карно для Q3

![]()

Для Q4 имеем карту Карно, представленную на рисунке 1.5.4.

|

Рисунок 1.5.4. Карта Карно для Q4

![]()

По полученным выражениям построена схема преобразователя кодов, изображенная на рисунке 1.5.5.

Преобразование параллельной формы представления числа в последовательную можно осуществить с помощью регистра сдвига.

Регистром называется устройство, выполняющее функции приёма, хранения, преобразования и передачи информации.

Кодовая комбинация с преобразователя кодов записывается в регистр сдвига параллельно по всем разрядам. Затем осуществляется сдвиг кода тактовыми импульсами, начиная со старшего разряда.

В данном курсовом проекте требуется синтезировать пятиразрядный регистр сдвига, выполненный на JK - триггерах.

На рисунке 1.6.1 приведена схема преобразователя параллельной формы представления числа в последовательную.

Для того, чтобы JK-триггер работал в режиме D-триггера необходимо на вход J подавать прямой сигнал, а на вход К – инверсный с помощью логического элемента НЕ.

На вход каждого триггера, кроме триггера, в который поступает младший

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.