Для реализации делителя частоты построим двоичный счётчик с последовательным переносом и коэффициентом счёта 3 на двух Т-триггерах. Зависимость выходных сигналов триггера от входных указана в таблице 1.3.

Таблица 1.3.

|

№ входящего импульса |

Q2 |

Q1 |

|

0 |

0 |

0 |

|

1 |

0 |

1 |

|

2 |

1 |

0 |

|

3 |

(1) 0 |

(1) 0 |

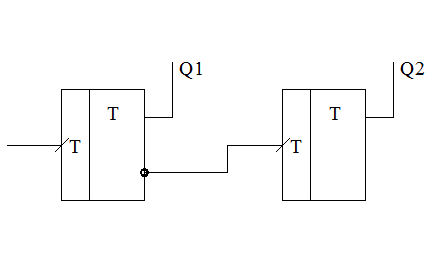

Необходимо подключить Т-триггеры как показано на рис.1.7

|

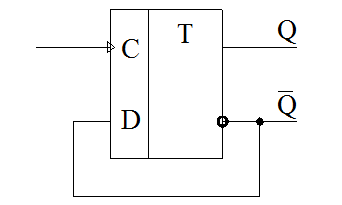

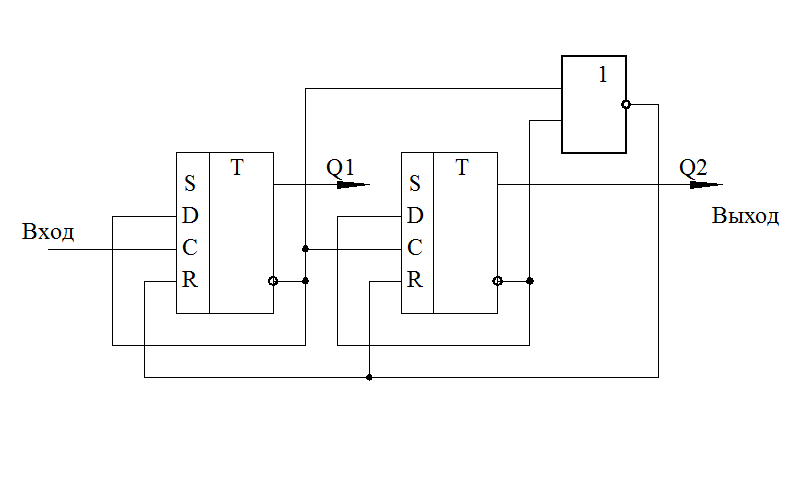

Для разработки схемы исключения устойчивого состояния определим двоичный код числа 3. Он равен 11. Учитывая, что базис реализации – ИЛИ-НЕ и представляя D-триггеры в качестве T-триггеров (рис. 1.8), построим искомую схему (рис. 1.9)

|

Рисунок 1.8

|

На рисунке 1.10 показаны временные диаграммы поясняющие работу делителя частоты.

C

t

|

|

|

|||||

A1

t

|

|

||||

A2

t

Рисунок 1.10.

Сумматоры служат для выполнения операций сложения и вычитания чисел, представленных в двоичной системе счисления.

Одноразрядным сумматором называется дискретное устройство, которое имеет три входа для подачи слагаемых аi, bi и переносов рi и реализуют операцию сложения по модулю два. На его выходах формируется сумма Si и перенос рi+1, предназначенный для передачи в следующий разряд.

Многоразрядный сумматор параллельного действия состоит из отдельных одноразрядных сумматоров, связанных между собой с помощью переноса. Каждый из одноразрядных сумматоров формирует на своем выходе цифру соответствующего разряда суммы и перенос, предаваемый на вход следующего, более старшего разряда.

В данном случае на каждый вход bi продублируем сигнал, выходящий из делителя частоты, а на входы аi будем подавать сигналы, выходящие из преобразователя кодов. Так как после преобразователя кодов будем иметь двоичное число, представленное в коде 3а+2 для кодирования которого требуется, пять разрядов, то сумматор параллельного действия должен состоять из четырех одноразрядных сумматоров.

Запишем таблицу истинности (ТИ) для одноразрядного сумматора (таблица 1.4), где

ai,bi — слагаемые;

pi — перенос входа;

pi+1 — перенос выхода;

Si — сумма.

|

Входы |

Выходы |

|||

|

ai |

bi |

pi |

Si |

Pi+1 |

|

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

0 |

1 |

0 |

|

1 |

0 |

0 |

1 |

0 |

|

1 |

1 |

0 |

0 |

1 |

|

0 |

0 |

1 |

1 |

0 |

|

0 |

1 |

1 |

1 |

0 |

|

1 |

0 |

1 |

1 |

0 |

|

1 |

1 |

1 |

1 |

1 |

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.