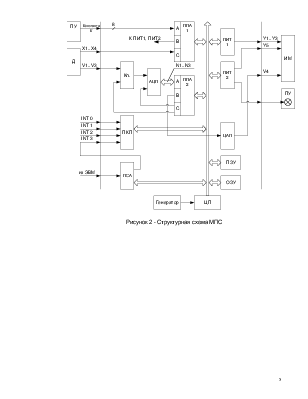

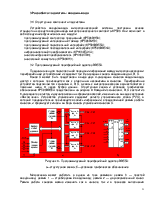

Младшая половина канала С ППА-1, настроенная на ввод информации ,используется для приема сигналов с датчиков Х1,Х2,X3,Х4.

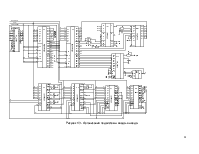

Распределение адресного пространства устройств ввода-вывода осуществляется с помощью микросхемы ПЗУ КР556РТ16 при наличии нулевого уровня на ADR15 и приведено в таблице 4.

Таблица 4 - Распределение адресного пространства устройств ввода-вывода

|

Адрес ПЗУ |

Содержимое ячейки |

Наименование Микросхемы |

|

E0h—E3h |

1h |

Программируемый интервальный таймер ПИТ1 КР580ВИ53 |

|

E4h—E7h |

2h |

Программируемый интервальный таймер ПИТ2 КР580ВИ53 |

|

E8h—EBh |

4h |

Программируемый периферийный адаптер ППА1 КР580ВВ55А |

|

ECh—EFh |

8h |

Программируемый периферийный адаптер ППА2 КР580ВВ55А |

|

F0h—F1h |

10h |

Программируемый связной адаптер ПСА КР580ВВ51А |

|

F4h—F5h |

20h |

Контроллер приоритетов прерываний КПП КР580ВН59А |

|

F8h |

40h |

Регистр индикации РИ1 |

|

FCh |

80h |

Регистр индикации РИ2 |

Реализация асинхронного канала связи МПС с удаленным терминалом осуществлена на основе БИС универсального синхронно-асинхронного приемопередатчика КР580ВВ51А.

Последовательный канал связи обеспечивает выдачу сигналов DTR и RTS к терминалу и прием сигналов DSR и CTS, задающих начало сеанса связи. Программно осуществляется обмен информацией между МПС и ЭВМ. В зависимости от запроса терминала (символы D или A), полученного по обратному каналу данных - от терминала к МПС, система выдает соответственно либо результат обработки цифровых датчиков Y1, либо результат обработки аналоговой информации Y4. Синхронизация работы БИС осуществляется с частотой 250 кГц, получаемой с выхода программируемого интервального таймера.

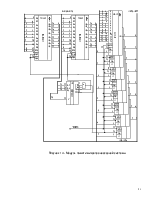

Рисунок 13 - Организация подсистемы ввода- вывода

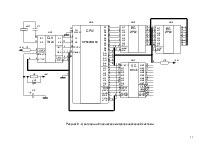

Данная микропроцессорная система должна иметь ПЗУ объемом 16 Кбайт. Адресное пространство (0000H-3FFFH). Для организации постоянной памяти используются микросхемы КР556РТ16 емкостью 8 Кбайт; таким образом, для обеспечения заданной емкости ПЗУ необходимо применение двух таких микросхем (0000H-1FFFH и 2000H-3FFFH), т.к для обеспечения требуемой информационной емкости ПЗУ необходимо наращивать память горизонтально.

Микросхема КР556РТ16 является БИС программируемого ПЗУ информационной емкостью 65536 бит с организацией 8192 8-разрядных байтов. По уровню и набору сигналов микросхема может использоваться для прямого подключения к системной шине микропроцессорной системы. Вход выборки кристалла CS – инверсный. Выходы данных БИС имеют три состояния и переходят в состояние высокого выходного сопротивления, не нагружающего шину системы, при неактивном сигнале CS. Микросхема имеет 13 адресных входов.

В данной системе необходимо построить ОЗУ емкостью 4 Кбайт (адресное пространство - 4000H-4FFFH) на микросхемах К541РУ1. Эти микросхемы являются статическими оперативными запоминающими устройствами на основе инжекционных структур. Микросхемы имеют информационную емкость 4096 бит с организацией 4096 слов по 1 разряду. Таким образом, для организации 4 Кбайт памяти необходимо применение восьми микросхем, т.к. для обеспечения требуемой разрядности схем ОЗУ осуществлено вертикальное наращивание памяти (увеличение разрядности).

Микросхемы имеют совмещенную для ввода и вывода информации шину данных с тремя состояниями; таким образом, возможно их прямое подключение к шине данных системы. Для выборки кристалла используется инверсный вход CS; для выбора режима работы – один вход WR, низкий уровень на котором говорит микросхеме о необходимости записи информации в ОЗУ с шины данных, высокий – о необходимости выдачи записанной информации на ШД. При высоком неактивном уровне на входе CS сигнал на входе WR может быть любым. Для выбора адреса слова микросхема имеет 12 адресных входов, напрямую подключаемых к шине адреса.

Логика выборки БИС реализована на схеме ТТЛ-дешифратора К155ИД12, на входы которого подаются разряды А14, А13 шины адреса. На вход разрешения дешифрации V подаётся 15-й бит с шины адресов (ADR15), если равен уровню логической единицы, то на выходе уровень логической единицы – дешифрация разрешена иначе - нет. Этим производится разделение адресного пространства ввода-вывода и подсистемы памяти. С выходов дешифратора через инвертор сигнал разрешения поступает на входы выбора микросхем памяти CS. Для ОЗУ режим работы определяется сигналом на входе WR/RD: единичный сигнал ¾ режим чтения, нулевой ¾ записи.

В ПЗУ размещены программы начальной инициализации системы, обработки данных, обслуживания прерываний. ОЗУ используется для хранения промежуточных данных в процессе

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.