Московский Энергетический Институт

(технический университет)

Курсовой проект

по дисциплинам

ФУиУ ЭВМ и СС МПТ

Студент

Группа А-7-99

Преподаватель

Москва

2003

Целью курсового проектирования является приобретение навыков разработки микропроцессорных систем (МПС) на примере проектирования микропроцессорной системы для управления некоторым объектом. МПС принимает информацию об объекте управления в виде входных сигналов от внешних аналоговых и цифровых датчиков, вырабатывает управляющие воздействия в соответствии с законом управления и подает их на исполнительный механизм. Также в МПС от ОУ поступают сигналы прерывания от датчика аварийной сигнализации и от датчика напряжения питания.

В ходе предварительной оценки поставленной задачи, были определены следующие основные принципы проектирования:

- минимизация аппаратных затрат;

- обеспечение возможности расширения управляющих алгоритмов и аппаратной конфигурации.

Основой МПС является однокристальная микроЭВМ (ОМЭВМ) КР1816ВЕ51[1, 2, 3].

Для построения схем управления будут использоваться ИМС серии КР1533[6].

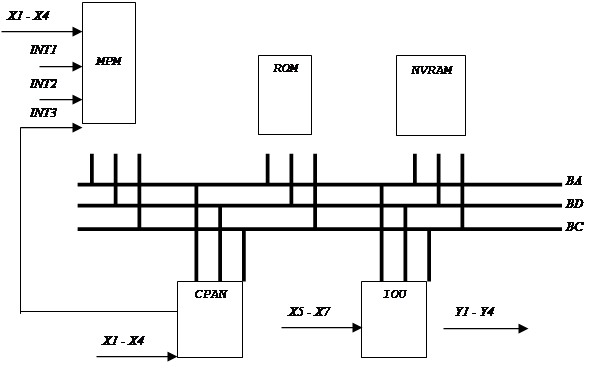

Структурная схема МПС приведена на рис. 1.

Принимаем для внешних двоичных сигналов Х1 – Х4, сигналов прерываний INT1, INT2, INT3 стандартные ТТЛ уровни, что даёт возможность их использования без каких-либо преобразований.

МПС состоит из следующих модулей, устройств и шин:

MPM — микропроцессорный модуль является центральным блоком системы. Включает в себя ОЭВМ КР1816ВЕ51, схему сброса. Т.к. ОЭВМ КР1816ВЕ51 содержит внутренние: оперативную память данных, РПЗУ программ, контроллер прерываний, 2 таймера/счётчика, то МПС не содержит отдельных модулей оперативной памяти, контроллера прерываний, таймера. Формирует сигналы адреса, управляющие сигналы. Обеспечивает обработку сигналов данных и внешних двоичных сигналов Х1 - Х4.

BA, BD, BC — шины адреса, данных и управления соответственно;

ROM — ПЗУ, содержит коды управляющей программы. Входными являются адресные и управляющие сигналы, выходными — сигналы данных;

NVRAM — энергонезависимое ОЗУ, предназначено для хранения информации о состоянии системы в случае отказа основного источника питания. Входными являются сигналы адреса, данных и управления, выходными — сигналы данных;

IOU — модуль интерфейсных устройств ввода-вывода предназначен для ввода напряжений Х5 - Х7 и вывода управляющих двоичных сигналов Y1 - Y3 и напряжения Y4. Входными являются указанные выше внешние сигналы, а также сигналы адреса, данных, управления, выходными — сигналы данных и управляющие сигналы;

CPAN — модуль управления и индикации содержит средства управления работой МПС, а также средства отображения значений Х1 - Х4 и Q4 и узел аварийной сигнализации. Входными являются сигналы адреса, данных, управления и внешние двоичные сигналы Х1 - Х4, выходными — управления и данных.

|

Рис. 1. Структурная схема МПС

В состав ОЭВМ КР1816ВЕ51 входит внутренняя программная память программ размером в 4Кб. Для того чтобы соблюсти условие и получить 20-ти кратный запас по памяти программ для дальнейшего возможного репрограммирования подключим внешнюю память.

ОЭВМ КР1816ВЕ51 допускает использование внешней программной памяти ёмкостью до 64Кб. Всё адресное пространство внешней программной памяти отведём под коды управляющей программы.

В состав ОЭВМ КР1816ВЕ51 входит внутреннее ОЗУ данных ёмкостью 128 Байт. Всё адресное пространство внутренней памяти данных отведём для хранения переменных управляющей программы.

ОЭВМ КР1816ВЕ51 допускает использование внешней памяти данных ёмкостью до 64Кб. В соответствии с техническим заданием используется отображение внешних и интерфейсных устройств на память, поэтому разобьём адресное пространство внешней памяти данных на две равные части в 32Кб. При этом одна часть используется для обращения к энергонезависимой памяти NVRAM, а другая — для обращения к внешним и интерфейсным устройствам. Для разделения используется линия адреса ВА15. Разделение адресного пространства внешней памяти данных с учётом

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.