Таким образом, в системе команд центрального процессора потребуется команда проверки состояния сопроцессора (конечно, ей окажется команда WAIT), а введение этих команд в объектную программу перед каждой командой сопроцессора могут осуществить ассемблер или компилятор языка высокого уровня автоматически без специальных указаний программиста.

Принципиально команду проверки и ожидания можно помещать и после каждой команды сопроцессора. Но в этом случае центральный процессор не будет выполнять никаких команд до тех пор, пока сопроцессор не освободится, и степень параллелизма работы обоих процессоров ухудшается.

Синхронизация по данным. Если выполняемая сопроцессором команда записывает операнд в ячейку памяти. перед последующей командой центрального процессора, которая обращается к этой же ячейке, также необходима аналогичная команда проверки состояния сопроцессора. В том случае, когда сопроцессор не успел записать результат в память до того, как он потребовался центральному процессору, последний должен ожидать завершения действий сопроцессора. Автоматически учесть такие ситуации довольно сложно, поэтому вводить команды, которые проверяют состояние сопроцессора и при необходимости заставляют центральный процессор ожидать, должен программист.

Когда команда сопроцессора требует дополнительных обращений к памяти, сопроцессор должен запрашивать шину у центрального процессора. При получении разрешения (или подтверждения запроса) сопроцессор самостоятельно инициирует обращение к памяти. Следовательно, в механизме взаимодействия центрального процессора и сопроцессора необходимы сигналы запроса/ разрешения шины.

На рис. 2.1 и 2.2 дано графическое пояснение действий центрального процессора и сопроцессора при выполнении команд программы. Выделенные линии на рис. 2.1 показывают, когда центральный процессор должен ожидать завершения действий сопроцессора.

Еще одна интерпретация совместной работы обоих процессоров во времени представлена на рис. 2.3. Фрагмент программы содержит команды центрального процессора и арифметического сопроцессора (они обозначены ЦП-i и АС-i соответственно). Правый столбец иллюстрирует действия центрального процессора, причем заштрихованные места соответствуют выполнению им команд сопроцессора, а левый — действия сопроцессора. Из рисунка видно, что к моменту начала выполнения команды АС-2 центральным процессором сопроцессор еще не закончил выполнять команду АС-1 и центральный процессор будет ожидать. Такая же ситуация возникает и при выполнении команды АС-2. Эти два случая соответствуют синхронизации по командам.

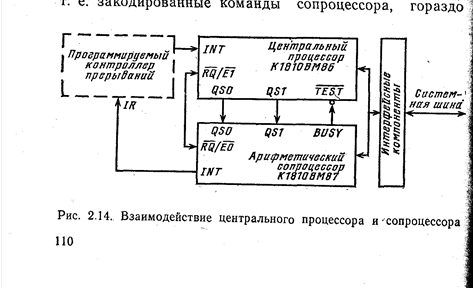

2.7. ВЗАИМОДЕЙСТВИЕ СОПРОЦЕССОРА И ЦЕНТРАЛЬНОГО ПРОЦЕССОРА

Сопроцессор представляет собой аппаратное расширение центрального процессора и не может работать ав тономно. Схема их совместных подключений приведена на рис. 2.14.Центральный процессор «выполнит» команду ESC, т. е. закодированные команды сопроцессора, гораздо

быстрее, чем сопроцессор закончит фактические действия этой команды. Например, команду FSQRT центральный процессор «выполняет» всего за 2 такта синхронизации, а сопроцессору требуются 180 тактов. Завершив команду ESC, центральный процессор дешифрует и выполняет следующие свои команды, а устройство управления сопроцессора повторяет его действия по выборке команд из очереди, но игнорирует команды центрального процессора. Следовательно, часть времени оба процессора работают параллельно, что повышает производительность системы.

Однако в двух ситуациях необходимо синхронизировать выполнение команд в сопроцессоре и центральном процессоре:

команда сопроцессора, к выполнению которой привлекается численное операционное устройство, не может начинаться до завершения им предыдущей команды;

центральный процессор не должен выполнять команду с обращением к операнду в памяти, адресуемому сопроцессором, до тех пор, пока сопроцессор не завершит обращение к требуемой ячейке.

Команда ожидания WAIT позволяет синхронизировать центральный процессор так, что он не будет «выполнять» следующую команду сопроцессора или свою команду до тех пор, пока сопроцессор не закончит текущую команду. Когда сопроцессор выполняет команду, он формирует на выходной линии BUSY высокий уровень напряжения. Эта линия подключена на вход TEST центрального процессора. При выполнении команды WAIT центральный процессор опрашивает сигнал на входе TEST и, пока им не будет сигнал низкого уровня, не переходит к следующей команде. Дешифрование команды, находящейся за командой WAIT, сопроцессор и центральный процессор осуществляют одновременно. Таким образом, для удовлетворения первого требования перед каждой

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.