Лабораторная работа №4

Изучение программируемого периферийного адаптера КР580ВВ55А

Цель работы: Изучить структуру и режимы работы программируемого периферийного адаптера ППА КР580ВВ55А, его программирование и возможности реализации простейших параллельных интерфейсов.

Передача информации будет осуществляться в режиме 0. Описание режима 0:

Данный режим позволяет осуществлять однонаправленный ввод ввод/вывод информации по всем трем портам (А,В,С). управляющее слово имеет вид:

|

1 |

0 |

0 |

PA |

PCH |

0 |

PB |

PCL |

где PA – режим работы порта А (1-ввод, 0- вывод)

PB – режим работы порта В (1-ввод, 0- вывод)

PCН – режим работы старшей тетрады порта С (1-ввод, 0- вывод)

PCL – режим работы младшей тетрады порта С (1-ввод, 0- вывод)

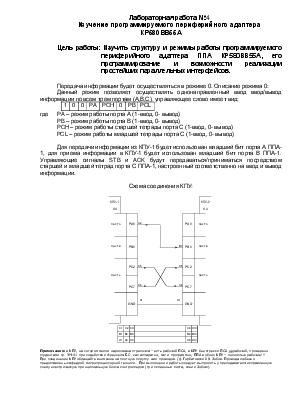

Для передачи информации из КПУ-1 будет использован младший бит порта А ППА-1, для приема информации в КПУ-1 будет использован младший бит порта В ППА-1. Управляющие сигналы STB и ACK будут передаваться/приниматься посредством старшей и младшей тетрад порта С ППА-1, настроенный соответственно на ввод и вывод информации.

Схема соединения КПУ:

Примечание: в КПУ, на котором мелом нарисована стрелочка – есть рабочий ПСА, в КПУ без стрелки ПСА нерабочий, проверено студентами гр. ЭМ-41 при содействии Френкеля Б.С. как аппаратно, так и программно, ППА в обоих КПУ – полностью рабочие!!!

При соединении КПУ обращайте внимание на плотную

скрутку жил проводов. (с) Горбатовский & Зобов. Провода любезно

предоставлены кафедрой микропроцессорной техники. При выполнении работы следует

выпросить у преподавателя исправленную схему электрическую принципиальную блока

контроллеров (три склеенных листа, клеил Зобов:)

Листинг Программы

1900 PA EQU F0H ;

1900 PB EQU F1H ;

1900 PC EQU F2H ;

1900 PPI EQU F3H ;

1900 DISP EQU E4H ;

ПЕРЕДАТЧИК

1900 16 14 INIT: MVI D,14H ; количество передаваемых байтов: 20

1902 21 00 1A LXI H,1A00H ; адрес начала передаваемого блока

1905 3E 8A MVI A,8AH ; Настройка ППА: порт А – вывод,

1907 D3 F3 OUT PPI ; порт В – ввод, порт СL – вывод, порт CH – ввод.

1909 0E 08 20BYTE: MVI C,08H ; количество передаваемых бит для одного байта

190B 7E 8BIT: MOV A,M ; чтение передаваемого байта

190C D3 F0 OUT PA ; вывод в порт А на передачу

190E 3E 04 MVI A,04H ; посылка подтверждающего сигнала STB

1910 D3 F2 OUT PC ; через порт С

1912 DB F2 ACK: IN PC ; Ожидание подтверждения приема

1914 E6 80 ANI 80H ; сигнал ACK

1916 FE 80 CPI 80H ; принимается через порт С

1918 C2 12 19 JNZ ACK ;

191B 3E 00 MVI A,00H ; сброс сигнала STB на линиях порта С

191D D3 F2 OUT PC ;

191F D3 F0 OUT PA ; обнуление порта А

1921 7E MOV A,M ; подготовка к сдвигу передававшегося байта

1922 0F RRC ; сдвиг

1923 77 MOV M,A ; сохранение сдвинутого байта обратно на его место

1924 0D DCR C ; уменьшение счетчика битов

1925 C2 0B 19 JNZ 8BIT ; если передано менее 8 бит – повтор передачи

1928 23 INX H ; переход к следующему байту

1929 15 DCR D ; уменьшение счетчика байт

192A C2 09 19 JNZ 20BYTE ; если передано менее 20 байт - повтор

192D 3E 37 END: MVI A,37H ; вывод на дисплей

192F D3 E4 OUT DISP ; подтверждение выполнения программы

1931 D3 E4 OUT DISP ;

1933 3E 77 MVI A,77H ;

1935 D3 E4 OUT DISP ;

1937 76 HLT ; останов

ПРИЁМНИК

1900 16 14 INTIT: MVI D,14H ; количество передаваемых байтов: 20

1902 21 00 1A LXI H,1A00H ; адрес начала передаваемого блока

1905 3E 8A MVI A,8AH ; Настройка ППА: порт А – вывод,

1907 D3 F3 OUT PPI ; порт В – ввод, порт СL – вывод, порт CH – ввод.

1909 0E 08 20BYTE: MVI C,08H ; количество передаваемых бит для одного байта

190B DB F2 8BIT: IN PC ; ожидание прихода сигнала STB

190D E6 80 ANI 80H ; от передатчика, прием производится через

190F FE 80 CPI 80H ; линии порта С

1911 C2 0B 19 JNZ 8BIT ;

1914 7E MOV A,M ; подготовка байта приема

1915 E6 FE ANI FEH ; обнуление младшего бита числа

1917 5F MOV E,A ; временное сохранение этого числа

1918 DB F1 IN PB ; прием информации в порт В

191A E6 01 ANI 01H ; выделение младшего бита в принятом байте

191C 83 ADD E ; добавление этого бита в младший бит байта приема

191D 0F RRC ; сдвиг байта приема

191E 77 MOV M,A ; запись байта приема на его первоначальный адрес

191F 3E 00 MVI A,04H ; посылка сигнала подтверждения приема ACK

1921 D3 F2 OUT PC ; через порт С

1923 DB F2 STB: IN PC ; ожидание снятия строба посылки

1925 E6 80 ANI 80H ; данных STB от передатчика

1927 FE 80 CPI 80H ;

1929 CA 23 19 JZ STB ;

192C 3E 00 MVI A,00H ; сброс сигнала ACK на линиях порта С

192E D3 F2 OUT PC ;

1930 0D DCR C ; уменьшение счетчика принятых бит

1931 C2 0B 19 JNZ 8BIT ; если меньше 8 – повтор приема

1934 23 INX H ; переход к следующему байту приема

1935 15 DCR D ; уменьшение счетчика принятых байт

1936 C2 09 19 JNZ 20BYTE ; если число байт меньше 20 - повтор

1939 3E 37 END: MVI A,37H ; вывод на дисплей

193B D3 E4 OUT DISP ; подтверждение выполнения программы

193D D3 E4 OUT DISP ;

193F 3E 77 MVI A,77H ;

1941 D3 E4 OUT DISP ;

1943 76 HLT ; останов

Примечание: Перед запуском программы в передатчике рекомендуется занести начиная с адреса 1А00h следующие значения: 11-22-33-44-55-66-77-88-99-AA-BB-CC-DD-EE-FF-11-22-33-44; в приемнике рекомендуется занести начиная с адреса 1А00h и по адрес 1A14h нули (00h).

Заключение: наличие встроенных средств ввода вывода информации в параллельном режиме у контроллера «Электроника МС2721» дает возможность передавать информацию, управлять различными цифровыми устройствами, получать информацию от объекта управления.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.