команды WAIT: анализ значений флажков слова состояния TS и

MP (исключительная ситуация 7, если оба флажка в 1);

8) для команды ESQ математического сопроцессора: анализ значений флажков слова состояния EM и TS (исключительная ситуация 7, если оба в 1);

9) проверка в указанном ниже порядке для каждого обращения к памяти, запрашиваемого командой:

а) проверка на наличие сегментных ошибок, которые препятствуют правильному преобразованию адресов памяти

(исключительные ситуации 11, 12, 13);

б) только для МП 80386: проверка на наличе страничных ошибок, которые препятствуют правильному преобразованию адресов памяти (исключительная ситуация 14).

При этом установлен порядок контроля, поддерживающий концепцию, что страничный механизм адресации должен быть "внизу" сегментного механизма адресации. Поэтому для любого полученного обращения к памяти (за кодом команды или за данными) анализ на исключительные ситуации, относящиеся к сегментному механизму адресации, будет выполняться до анализа на исключительные ситуации, относящиеся к страничному механизму адресации.

-------------¬

¦ Регистры ¦

L------------- Микропроцессор 80286 имеет четыре набора регистров:

1) регистры общего назначения;

2) сегментные регистры;

3) указатель команды, флажки и слово состояния машины (MSW);

4) системные регистры:

регистры системных адресов и регистры системных сегментов.

На рис. 3.2-3.6 приведен весь набор регистров микропроцессора 80286, который полностью задействован только в защищенном режиме.

----------------------------¬

¦Регистры общего назначения ¦

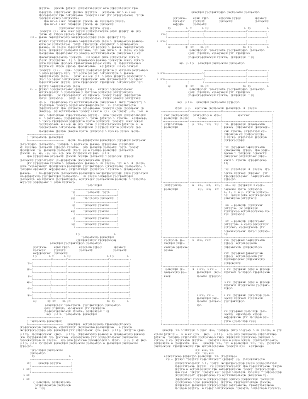

L---------------------------- Восемь регистров общего назначения

(часто их для краткости именуют также "общие регистры") имеют длину 16 бит и используются для хранения адресов или данных. Они используются для хранения данных длиной 1, 8, 16 и (при использовании двух регистров) 32

бит; разрядных полей от 1 до 16 бит; адресов длиной 16 бит. Эти регистры показаны на рис. 3.2 и называются AX, BX, CX, DX, SI, DI, BP, SP.

7 0 7 0

------------T------------¬ --¬

AX ¦ AH ¦ AL ¦ ¦ Аккумулятор в командах

+-----------+------------+ ¦- умножения, деления, вводаDX ¦ DH ¦ DL ¦ ¦ вывода

+-----------+------------+ --CX ¦ CH ¦ CL ¦ ---- Счетчик в командах: циклов,

+-----------+------------+ --¬ сдвигов, повторений

BX ¦ BH ¦ BL ¦ ¦

+-----------+------------+ ¦- Регистры базы

BP ¦ Указатель базы ¦ ¦

+------------------------+ --+

SI ¦ Индекс источника ¦ ¦

+------------------------+ ¦- Индексные регистры,

DI ¦ Индекс приемника ¦ ¦ указатели в строковых командах

+------------------------+ --SP ¦ Указатель стека ¦

L------------------------15 0

Рис. 3.2. Регистры общего назначения

------------------¬

¦Указатель команд ¦

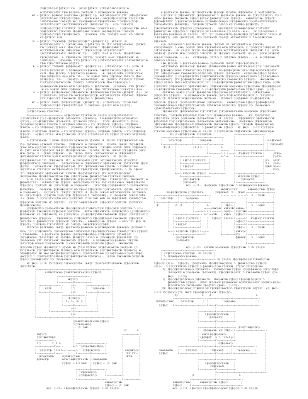

L------------------ Указатель команд (IP) является 16-разрядным регистром. Он содержит относительный адрес следующей команды, подлежащей выполнению. Регистр указателя команд приведен на рис 3.3.

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

---------------------¬ ---T--T--T--T--T--T--T--T--T--T--T--T--T--T--T--¬

FLAGS¦ Флажки ¦->¦//¦NT¦ IOPL¦OF¦DF¦IF¦TF¦SF¦ZF¦//¦AF¦//¦PF¦//¦CF¦

+--------------------+ L--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--IP¦ Указатель команды ¦ 15 3 2 1 0

+--------------------+ ---T--T--T--T--T--T--T--T--T--T--T--T--T--T--T--¬

MSW¦ ¦->¦//¦//¦//¦//¦//¦//¦//¦//¦//¦//¦//¦//¦TS¦EM¦MP¦PE¦

L--------------------- L--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--15 0

Где:

---¬

¦//¦ - резерв;

L--MSW - слово состояния машины.

Рис. 3.3. Регистр указателя команд, флажки и слово состояния машины (MSW)

----------------¬

¦Регистр флажков¦

L---------------- Регистр флажков (FLAGS) участвует в управлении вводом-выводом, маскируемыми прерываниями, отладкой, переключением задач в защищенной многозадачной среде. Вместе с этими флажками в FLAGS есть разряды, которые отражают результат выполнения команды.

Назначение разрядов регистра флажков (см. рис. 3.3) микропроцессора

80286 в основном совпадает с их назначением в микропроцессоре 8086, за исключением двух флажков: NT и IOPL, которые являются новыми и используются только в защищенном режиме.

Флажки состояния (отражают результат выполнения команды):

CF - флажок переноса из старшего разряда (разряд 0). CF установлен, если в результате выполнения операции произошел перенос

(сложение) или заем (вычитание) из самого старшего разряда. В

противном случае CF сброшен. Для 8-, 16-разрядных операций CF

устанавливается согласно переносу/заему соответственно из разрядов 7, 15;

AF - флажок вспомогательного переноса (разряд 4). Флажок вспомогательного переноса упрощает сложение чисел в упакованном формате BCD. AF установлен, если в результате выполнения операции возник перенос (сложение) из разряда 3 или заем

(вычитание) из разряда 3. В противном случае AF сброшен. AF

устанавливается согласно переносу или заему в разряд 3

независимо от того, какова длина операндов - 8 или 16 разрядов;

OF - флажок переполнения (разряд 11). OF установлен, если в результате выполнения операции возникло знаковое переполнение.

Знаковое переполнение возникает, когда в результате выполнения операции в знаковый разряд (самый старший) результата заносится перенос/заем, но он выходит за пределы самого старшего разряда.

Для 8-, 16-разрядных операций OF установлен согласно переполнению соответственно в разрядах 7, 15;

ZF - флажок нуля (разряд 6). Он установлен, если все разряды результата равны нулю, а в противном случае сброшен;

SF - флажок знака (разряд 7). Он установлен, если установлен самый старший разряд результата, а в противном случае сброшен. Для

8-, 16-разрядных операндов SF соответственно отражает состояние разрядов 7, 15;

PF - флажок паритета (четности, разряд 2). PF установлен, если 8

самых младших разрядов результата операции содержат четное число единиц (четный паритет). PF сброшен, если 8 самых младших разрядов имеют нечетный паритет.

Флажки управления:

DF - флажок направления (разряд 10), указывает направление прохождения цепочек в строковых командах (0 - в направлении увеличения, 1 - в направлении уменьшения адреса). При выполнении строковых команд в DF задается последующее увеличение на 1 или уменьшение на 1 содержимого индексных

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.