Министерство образования Республики Беларусь

БЕЛОРУССКИЙ ГОСУДАРСТВЕННЫЙ

УНИВЕРСИТЕТ ТРАНСПОРТА

Кафедра микропроцессорной техники

и информационно-управляющих систем

Анализ безопасных

микроэлектронных схем

железнодорожной автоматики

Методические указания к лабораторным работам

по дисциплине “Микропроцессорные

информационно-управляющие системы”

Гомель 1999

Министерство образования Республики Беларусь

БЕЛОРУССКИЙ ГОСУДАРСТВЕННЫЙ

УНИВЕРСИТЕТ ТРАНСПОРТА

Кафедра микропроцессорной техники

и информационно-управляющих систем

С. Н.

Анализ безопасных

микроэлектронных схем

железнодорожной автоматики

Методические указания к лабораторным работам

по дисциплине “Микропроцессорные

информационно-управляющие системы”

Одобрено методической комиссией электротехнического факультета

Белорусского государственного университета транспорта

Гомель 1999

УДК

Х211

Х211 Анализ безопасных микроэлектронных схем железнодорожной автоматики: Методические указания к лабораторным работам по дисциплине “Микропроцессорные информационно-управляющие системы на транспорте”/ Белорус. гос. ун-т трансп. – Гомель: БелГУТ, 1999. – с.

Рассмотрены основные принципы обеспечения безопасности микроэлектронных схем железнодорожной автоматики, методы их анализа с помощью пакета Electrionics Workbench. Предназначены для студентов специальности “Автоматика, телемеханика и связь на транспорте”.

Рецензент – канд. техн. наук доцент В. С. Смоленчук

© С.Н.

ВВЕДЕНИЕ

Целью данного цикла лабораторных работ является изучение принципов построения и получение практических навыков создания надежных отказоустойчивых схем сопряжения микропроцессорных систем, связанных с обеспечением безопасности, с исполнительными объектами. Рассмотрены способы реализации различных схемных решений и проверки их работоспособности на базе пакета Electonics Workbench.

Порядок анализа каждой схемы подробно рассматривается в конкретной лабораторной работе.

Л а б о р а т о р н а я р а б о т а № 1

Ц е л ь р а б о т ы.Изучить схему коллекторно-базовой логики.

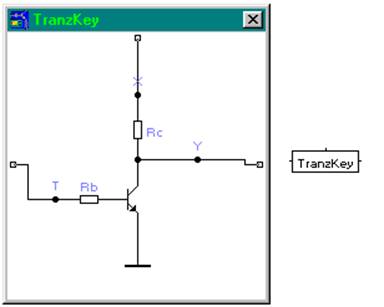

Коллекторно-базовой логикой называют схемы на основе транзисторных ключей, где сигналы подаются на базу и коллектор транзистора.

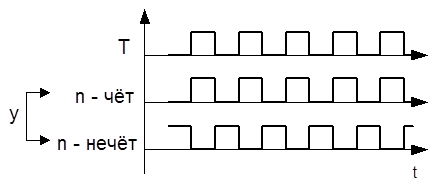

Многовходовой логический элемент безопасности основан на каскадном включении нескольких транзисторных ключей. На базовый вход первого ключа подаются импульсы Т. При наличии на всех коллекторных входах высоких потенциалов на выходе последнего ключа в зависимости от их количества получается импульсный сигнал той же (при чётном) или обратной (при нечётном) фазы. Такой схемой реализуется функция алгебры логики y= x1 x2… xn .

На рисунке 1 представлена схема транзисторного ключа, а на рисунке 2 — диаграммы работы каскада при различном n.

|

|

Рисунок 2. Диаграмма работы схемы при различных n

Для анализа безопасности схем используется программный пакет Electronics Workbench 4.* (EWb ).

Для создания схемы в помощью EWb элементы поштучно выбираются в закладках, соответствующих характеру элемента (активные, пассивные, полевые транзисторы, управляющие и т.д.) и переносятся на рабочее поле EWb, где далее соединяются согласно исследуемой схеме. Для изменения параметров элемента необходимо дважды щелкнуть на нем. Присвоение элементу обозначения производится нажатием клавиш Ctrl+L.

Для эмуляции отказов и сбоев в схеме удобно использовать переключатели (закладка “Управляющие”/“Control”). Примеры эмуляции элементов с возможностью отказа приведены ниже.

Для проверки схема снабжается контрольными приборами (осциллографом; амперметрами и вольтметрами из закладки “Индикаторы”) в необходимом количестве.

Включается схема нажатием на выключатель либо клавишами Ctrl+G. Далее ведется наблюдение за работой схемы, по приборам отслеживаются и заносятся в отчёт необходимые данные.

Далее будет рассмотрена эмуляция различных элементов приведённой схемы с помощью EWb. Для каждого элемента приведён рисунок, поясняющий схему эмуляции, и таблица, в которой указаны возможные состояния элемента и соответствующее положение ключей.

Рассмотрим эмуляцию работы резистора. Возможны следующие режимы работы: нормальная работа, обрыв соединения, пробой резистора на незначительное сопротивление.

|

Рисунок 3. Эмуляция резистора

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.