3. Много ли промежуточных данных Да

Нет

4. Ожидается ли модификация Да

Нет

5. Требуется ли функциональная гибкость

6. Анализируется : достаточно ли высокое быстродействие у микропроцессорного устройства.

Если да, то используется микропроцессорное управляющее устройство, нет - схема с жесткой логикой.

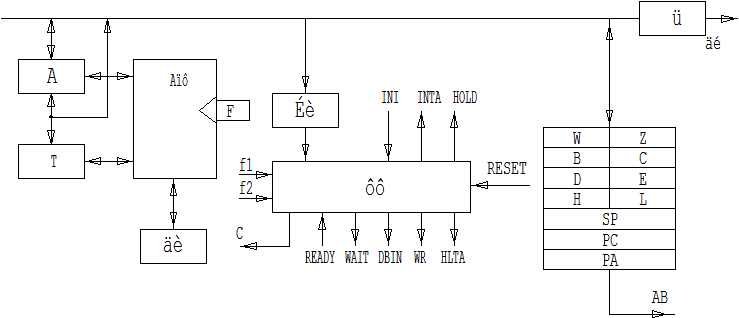

Архитектура МП I8080 (KP580BM80A)

Архитектура это представление МП и его устройства с точки зрения программиста. Она состоит из регистровой модели устройства и внешних управляющих сигналов.

Основные функциональные блоки:

АЛУ арифметико-логическое устройство - чисто комбинационная схема, которая выполняет операции над 8-ми разрядными данными аккумулятора и регистра временного хранения (Т).

Все эти операции выполняет по микрокомандам устройство управления(УУ) результат помещается в аккумулятор . АЛУ может выполнять бинарные и унарные операции. В унарных участвует один аккумулятор. Результаты отражаются в регистре флагов(F). Аккумулятор выполняет следующие операции:

1) Сложение, вычитание над целыми двоичными числами. Если в результате получилось отрицательное число, то оно будет представлено в дополнительном коде.

Пример:

Допустим необходимо представить число 1001 в дополнительном коде, для этого:

1. проинвертируем его 0110

2. добавим единицу 0111

Получили дополнительный код.

2) Коньюнкция, дизъюнкция, сложение по модулю 2.

3) Инверсия аккумулятора, инкремент, декремент, логический сдвиг 8-ми разрядов, циклический сдвиг 9-ти разрядов и обнуление.

К АЛУ может подключаться блок десятичной коррекции (ДК). Этот блок позволяет выполнять операции сложения над двоично-десятичными кодами.

|

0 0 0 0 |

1 0 0 1 + 1 |

09 |

|

1 0 1 0 |

0А |

|

|

0 0 0 1 |

0 0 0 0 |

10 |

Регистр общего назначения РОН

Регистры B,C,D,E,H,L используются как сверх-оперативная память МП. Обращение к этим регистрам выполняется без активации внешних сигналов.

Регистры W,Z используются для промежуточного хранения адреса, и прямой адресации.

Регистры могут объединяться в группы по парам (B-C, D-E, H-L), - регистровые пары используются при косвенной адресации. (т.е. для промежуточного хранения адреса).

SP(регистр стека) - регистр, специализированный по указатель стека.

Стек - специальная область памяти, организованная по принципу LIFO(последний вошёл первый вышел)

PC - програмный счётчик (следит за извлечением команды из памяти)

БРА(РА) - буферный регистр адреса.

УУ различает регистры команды(76 кодов операций). Обработка этих кодов выполняется по сигналам тактирования f1 и f2 в течении одного командного цикла при выполнении команд цикла выполняются внутренние кодциклы (машинные циклы), специализируются на следующих действиях:

1) Чтение кода команды из памяти РК

2) Чтение памяти ( по этому циклу выполняется пересылка памяти в любой регистр). R¬(П)

3) Запись в память. R®(П)

4) Чтение устройства ввода-вывода (УВВ). А¬(port)

5) Запись устройства ввода-вывода.A®(port)

6) Чтение стека. RP(ST)

7) Запись в стек. RP(ST)

8) HLT (обслуживание останова)

9) INTA (обслуживание прерывания)

10) INTA/HLT (обслуживание прерывания во время останова)

Командный цикл может содержать от 1 до 5 машинных циклов, причём, первым всегда выполняется цикл чтения команды. Каждый машинный цикл выполняется за время от 3 до 5 машинных тактов. В начале каждого машинного цикла УУ вырабатывает сигнал внешней синхронизации (с). Во время этого сигнала на шину данных выставляется машинный код ( идентификатор типа машинного цикла). Слово состояния процессора используется для формирования сигнала управления с помощью специального системного контроллера.

УУ имеет блок синхронизации, блок управления периферийными устройствами, блок прерываний, блок захвата и блок начальной установки.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.