|

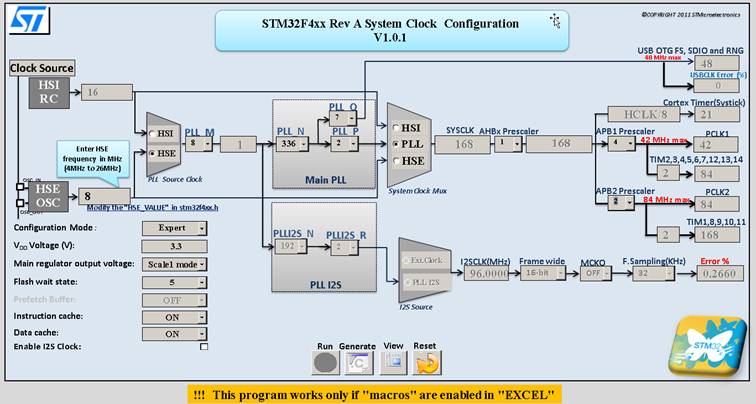

Система тактирования микроконтроллеров STM32F4xx. Система тактирования формирует ряд независимых сигналов для тактирования ядра и периферийных устройств микроконтроллера. Большинство сигналов, формируемых системой тактирования, являются производными от сигнала SYSCLK (system clock). На нижеследующем рисунке показана схема формирования сигнала SYSCLK и производных от него сигналов. В качестве источника импульсов тактовой системной частоты (SYSCLK) микроконтроллеров STM32F4xx могут быть использованы: внутренний RC-генератор (HSI), генератор HSE с внешним кварцевым резонатором или внешним источником тактовых импульсов, система фазовой автоподстройки частоты. Генератор HSI (High-Speed Internal) представляет собой встроенный RC-генератор с частотой 16 МГц, калиброванный в процессе производства с точностью ±1%. Для компенсации воздействия окружающей температуры и изменений питающего напряжения имеется возможность дополнять заводское калибровочное значение. Генератор HSE представляет собой встроенный генератор способный работать с кварцевыми и керамическими резонаторами на частотах от 4 до 24 МГц или c внешним источником тактовых импульсов частотой до 24 МГц и скважностью 50% Система фазовой автоподстройки частоты (PLL) позволяет устанавливать частоту сигнала SYSCLK как ниже, так и выше частоты сигнала на входе PLL, но не более 168 МГц. 168 МГц максимальная рабочая частота микроконтроллеров STM32F4xx.

Из сигнала SYSCLK путем деления его на коэффициент N = 1, 2, 4, .., 512 формируется сигнал HCLK для тактирования высокоскоростных шин AHB1-AHB3. В свою очередь, сигнал HCLK используется для формирования сигналов тактирования PCLK1 и PCLK2 низкоскоростных шин APB1 и APB2. Для формирования сигнала тактирования PCLK1 и PCLK2 у каждой шины имеется свой делитель с программируемым коэффициентом деления K = 1, 2, 4, 8 или 16. Коэффициенты деления для шин APB1 и APB2 устанавливаются независимо. Система тактирования формирует тактовые сигналы для 15 таймеров, входящих в состав микроконтроллера. Системный таймер SysTick подключен к шине AHB. Тактовый сигнал для него формируется из сигнала HCLK путем деления частоты сигнала HCLK на 8. Остальные 14 таймеров разделены на две группы. Одна группа подключена к шине APB1, а вторая к шине APB2. Для каждой группы таймеров формируется свой тактовый сигнал. Частота тактового сигнала таймеров, подключенных к шине APB, привязана к частоте PCLK и связана с ней следующим образом. Обозначим частоту сигнала HCLK как FHCLK. Тогда, в зависимости от выбранного коэффициента деления, частота сигнала PCLK и частота сигнала тактирования таймеров определяются следующими выражениями: FPCLK= FHCLK/1, FHCLK/2, FHCLK/4, FHCLK/8, FHCLK/16, FTCLK= FHCLK/1, FHCLK/1, FHCLK/2, FHCLK/4, FHCLK/8. Т.е., при установке частоты тактирования шины APB устанавливается и соответствующая ей частота тактирования таймеров, подключенных к этой шине. |

При программировании микроконтроллеров STM32F4xx необходимо сконфигурировать систему тактирования микроконтроллера. Функции для конфигурирования находятся в файле system_stm32f4xx.c. В процессе конфигурирования как минимум необходимо выбрать источник тактирования, коэффициенты деления PLL (если PLL используется), коэффициенты деления делителей шин AHB, APB1 и APB2. Фирма STMicroelectronics разработала программу STM32F4xx_Clock_Configuration_V1.0.1.xls, которая позволяет упростить процесс конфигурирования микроконтроллера. По сути, эта программа является макросом для Excel.

Запустим программу и сконфигурируем систему тактирования для макетной платы STM32F4DISCOVERY. Откроется следующее окно. Программа можетработать в двух режимах: режиме

Expert и режиме Wizard. Перейдем в режим Expert. На плате STM32F4DISCOVERY установлен кварцевый резонатор на частоту 8 МГц. Установим частоту генератора HSE OSC равную 8 МГц, выберем в качестве источника сигнала SYSCLK систему фазовой автоподстройки PLL, и выберем коэффициенты деления делителей PLL такими, чтобы получить максимально допустимую частоту сигнала SYSCLK 168 МГц:

PLL_M=8, PLL_N=336, PLL_P=2, AHBx Prescaler=1, APB1 Prescaler=4, APB2 Prescaler=2.

В результате получим следующие тактовые частоты:

SYSCLK=168 МГц, HCLK=168 МГц, PCLK1=42 МГц, PCLK2=84 МГц.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.