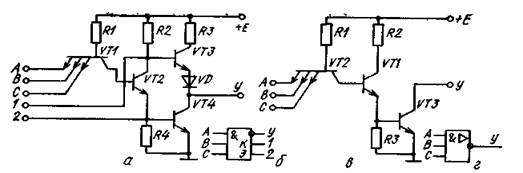

Базовые интегральные ТТЛ-схемы имеют два вида выходов (рис. 1): с резистором в коллекторе выходного транзистора и с открытым коллектором. Выход с открытым коллектором, во-первых, позволяет иметь много параллельных выходов, что обеспечивает логическое сложение выходных функции схем при подаче напряжения питания на группу соединенных вместе выходов через резистор соответствующего сопротивления, которое зависит от числа соединенных выходов и числа подключенных к ним входов последующих элементов. Во-вторых, выход с открытым коллектором дает возможность использовать ТТЛ-схемы в качестве усилителей индикации.

Рис. 1 Базовые интегральные ТТЛ-схемы с резистором в коллекторе выходного транзистора (а), с открытым коллектором (в) и их условные обозначения (б, г)

Основной особенностью элементов ТТЛ является использование в них многоэмиттерных транзисторов (МЭТ). Если на все входы МЭТ VT1 поданы напряжения, соответствующие уровню логической единицы, то ток через резистор R1 течет в базу транзистора VT2, а затем усиленный ток с эмиттера VT2 поступает в базу выходного инвертирующего транзистора VT4, открывая его; при этом транзистор VT3 будет закрыт и напряжение на выходе у будет соответствовать уровню логического нуля. Если хотя бы на одном входе МЭТ появится входное напряжение, соответствующее уровню логического нуля, то откроется соответствующий переход база—эмиттер, МЭТ перейдет в состояние насыщения и потенциал его коллектора станет близким к нулю. Следовательно, VT2 закроется, VT3 откроется, а на выходе у схемы установится напряжение, соответствующее уровню логической единицы

Схема на рис. 1, на транзисторах VT2—VT4 реализован сложный инвертор, осуществляющий операцию «НЕ», что позволило обеспечить высокую нагрузочную способность, достаточное быстродействие и помехоустойчивость схемы, поскольку ток в выходной цепи в закрытом состоянии схемы создается малым выходным сопротивлением эмиттерного повторителя, собранного на транзисторе VT3, а в открытом состоянии ток, поступающий в схему, обеспечивается малым выходным сопротивлением открытого транзистора VT4.

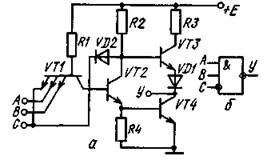

Рис 2 Схема И—НЕ с тремя состояниями (а)

Кроме рассмотренных ТТЛ-схем, выпускаются схемы с тремя состояниями для обеспечения совместной работы с линиями магистралей (рис. 2). Название этих схем может ввести в заблуждение, так как на самом деле они не являются логическими элементами с тремя уровнями напряжений. Это самые обычные логические схемы, которые имеют третье состояние выхода — «обрыв». Они совмещают в себе все преимущества элементов с резистором в цепи нагрузки и способность работать на общую шину, которой обладает схема с открытым коллектором. Схемы с тремя состояниями имеют отдельный запирающий вход С, с помощью которого они могут устанавливаться в третье состояние независимо от того, какие сигналы действуют на логических входах Ввиду улучшенных характеристик их используют обычно в качестве шинных формирователей вместо схем с открытым коллектором. Устанавливать нагрузочный резистор в этом случае не требуется.

Схема, изображенная на рис. 2, а, реализует функцию И—НЕ и работает следующим образом. Для управления транзисторами VT3 и VT4 тут введена дополнительная управляющая цепь, которая называется управлением (вход С). Этот вход через диод VD2 подключен к базе транзистора VT3, а также к эмиттеру МЭТ VT1.

Когда на вход С поступает напряжение, соответствующее уровню логического нуля, транзисторы VT3 и VT4 закрыты (VT3 закрыт потому, что на его базе в этом случае будет низкий потенциал, a VT4 из-за того, что на эмиттер VT1 подан логический нуль). Если на вход-С подать высокий потенциал, то диод VD2 будет закрыт и транзистор VT3 будет работать как в обычной ТТЛ-схеме. Таким образом, когда на вход С подан высокий потенциал, состояние схемы будет определяться другими входами и она работает как обычная ТТЛ-схема, реализующая функцию И—НЕ.

Схемы повторения и некоторые инверторы служат для подачи более высоких питающих напряжений, превышающих заданное для серии ТТЛ напряжение 5В, а также для увеличения нагрузочной способности вентилей свыше типового значения.

Преимуществами схем на КМОП-транзисторах являются малая потребляемая мощность, высокое быстродействие и повышенная помехоустойчивость. В основе всех логических КМОП-схем лежит КМОП,-инвертор (рис. 3, а). Здесь VT1 — транзистор с каналом n-типа, VT2 — с каналом р-типа. Затворы обоих транзисторов объединены, на них подается управляющее напряжение. Подложки соединены с истоками.

При поступлении на вход напряжения высокого уровня (логической единицы) открывается транзистор VT1, a VT2 закрывается. Наоборот, при подаче на вход напряжения, соответствующего уровню логического нуля, открывается транзистор VT2, a VT1 закрывается. Высокое быстродействие таких схем реализуется за счет того, что в цепях заряда и разряда паразитных емкостей схемы включены малые сопротивления открытых транзисторов. Схема, реализующая функцию ИЛИ—НЕ показана на рис. 4. При поступлении на вход А напряжения, соответствующего уровню логической единицы, открывается транзистор VT1 и закрывается VT4, в результате чего напряжение на выходе будет соответствовать уровню логического нуля (у = 0). При подаче на входы А и В напряжения, соответствующего уровню

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.