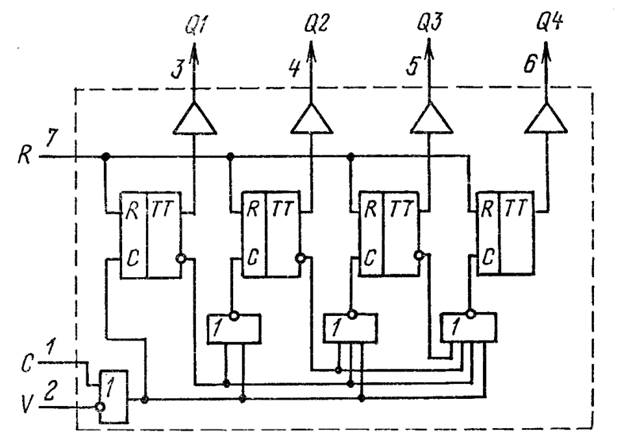

содержит два независимых 4-разрядных двоичных счетчика с параллельным выходом. Для повышения быстродействия в ИС применен параллельный перенос во все разряды. Подача счетных импульсов может производиться либо в положительной полярности (высоким уровнем) на вход С, либо в отрицательной полярности (низким уровнем) на вход V. В первом случае разрешение счета устанавливается высоким уровнем на входе V, а во втором случае – низким уровнем на входе С.

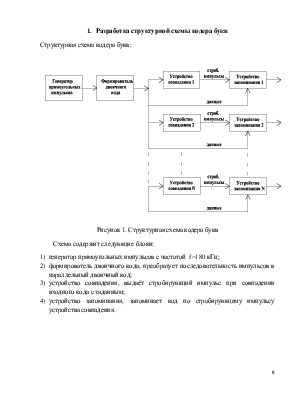

Рисунок 4.1. Структурная схема и условное обозначение счетчиков типа ИЕ10

Рисунок 4.2. Условное обозначение

Рисунок 4.2. Условное обозначение

При построении многоразрядных счетчиков с числом разрядов более четырех соединение между собой ИС ИЕ10 может производиться с последовательным или параллельным формированием переноса. В первом случае на вход С (вывод 1 или 9) следующего каскада счетчика подается высокий уровень с выхода Q4 (выводы 6 или 14) предыдущего каскада.

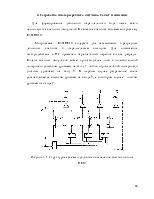

Схемная реализация счётчика приведена на рисунке 4.3.

Рисунок

4.3. Схемная реализация счетчика

Рисунок

4.3. Схемная реализация счетчика

Так как счетчик по условию должен быть 5-ти разрядным, то обнуляем счетчики высоким уровнем на 13-й ножке.

Таблица 4.1.Основные предельно-допустимые и электрические параметры К561ИЕ10

|

Uи.п., В |

U0вых, В |

U1вых, В |

I0вых, мA |

I1вых, мA |

fmax, МГц |

Iпот, мкА |

|

5 |

0,8 |

4.2 |

0.2 |

0,2 |

2 |

50 |

5. Схема преобразователя букв в двоичный код

Схемы преобразователя букв в двоичный код можно построить следующими способами:

1) записать булево выражение для каждой буквы фамилии с именем, привести его к необходимому базису и реализовать на логических элементах;

2) использовать дешифратор, при этом выходные сигналы необходимо снимать с выходов дешифратора, номера которых соответствуют коду буквы фамилии с именем.

Первый способ простой, но требует использования большого количества логических элементов. Второй способ универсален, так как сигнал можно снимать с любого из выходов дешифратора, но требует использования пятиразрядного дешифратора.

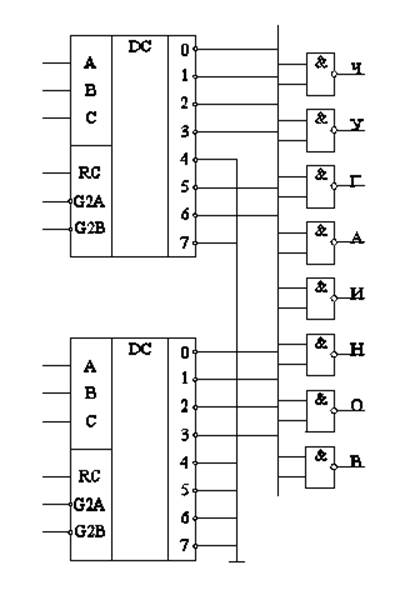

В КМОП - серии К561 нет микросхем пятиразрядного дешифратора. Поэтому воспользуемся схемой матричного дешифратора, реализованного на двух трёхразрядных дешифраторах. Схему преобразователя букв в двоичный код построим следующим способом: используем дешифратор, при этом выходные сигналы необходимо снимать с выходов дешифратора, номера которых соответствуют коду буквы фамилии с именем. Этот способ универсален, так как сигнал можно снимать с любого из выходов дешифратора. В качестве дешифраторов будем использовать микросхему К561ИД7, УГО и цоколёвка которого представлены на рисунке 5.1.

Рисунок 5.1 УГО

и цоколёвка К561ИД7

Рисунок 5.1 УГО

и цоколёвка К561ИД7

|

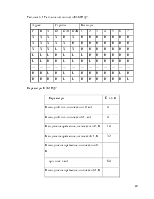

Таблица 5.1 Таблица истинности К561ИД7.

Параметры К561ИД7

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

МикросхемаИД7 - дешифратор, имеющий три адресных входа А, В, С, три входа стробирования G1, G2A, G2B, два из которых инверсные (G2A, G2B), и восемь инверсных выходов. Логический 0 на одном из выходов может появиться лишь при единственном разрешающем сочетании сигналов на входах стробирования - на инверсных входах должен быть логический 0, на прямом - логическая 1.

При всех других сочетаниях сигналов на входах стробирования на всех выходах микросхемы -логический 1. Сигнал логического 0 при разрешающем сочетании на входах появится на том выходе дешифратора, номер которого соответствует десятичному эквиваленту кода, поданному на адресные входы А, В, С.

Так как выходы дешифратора инверсные, то для получения выходного сигнала необходимо использовать логические элементы 2И – НЕ. Для этого выбираем 2 микросхемы К561ЛА5.

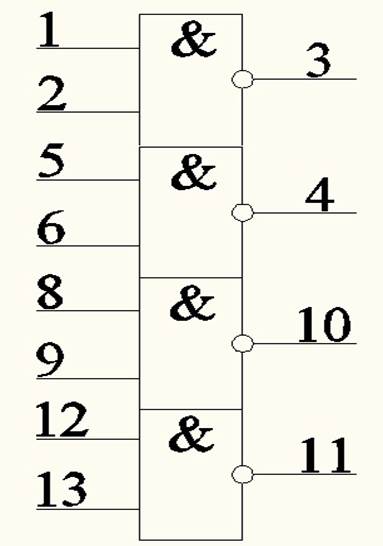

Рисунок 5.2 Микросхема типа К561ЛА5

Микросхемы типа К561ЛА5 выполняют логическую функцию 2И-НЕ. Реализация ее обеспечивается последовательным соединением МДП-транзисторов с каналом р-типа и параллельным соединением МДП-транзисторов с каналом n-типа. Так как букв шесть, то нужно взять 2 микросхемы для реализации нужного количества букв.

Основные параметры:

![]()

![]()

![]()

![]()

![]()

![]()

Составим схему неполного матричного дешифратора:

Рисунок 5.3 Схема совпадения кодов на неполном матричном дешифраторе

6. Разработка линейки выходных регистров памяти

Устройство памяти представляет собой 6 регистров, с параллельно соединенными входами данных одинаковой разрядности.

Регистровую память реализуем на микросхеме К561ИР6. В качестве регистров памяти (DD8 – DD13) применена микросхема К561ИР

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.