10.Укрупненная структура ЦСП TMS320F2812. Внутренняя шинная организация. Модифицированная гарвардская архитектура.

Внутренняя система шин включает в себя 2 составные шины:

1) шина чтения программ (22-разрядная адресная шина и 32-разрядная шина данных);

2) шина чтения и записи данных (32-разрядная адресная шина и 32-разрядная шина данных).

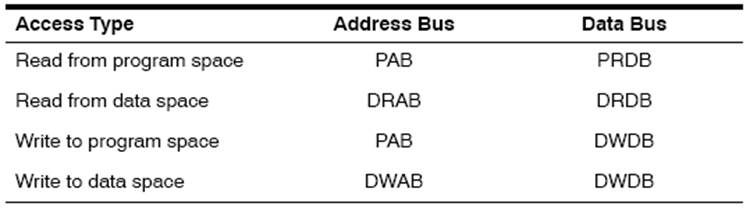

Функционально внутренняя шинная организация ЦСП F2812 включает в себя:

три адресные шины:

PAB (Program address bus, 22 бита – адресует программную память для чтения и записи);

DRAB (Data-read address bus, 32 бита – адресует память данных для чтения);

DWAB (Data-write address bus, 32 бита – адресует память данных для записи);

три шины данных:

PRDB (Program-read data bus, 32 бита – передает инструкции или данные во время чтения из программной памяти);

DRDB (Data-read data bus, 32 бита – передает данные во время чтения из памяти данных);

DWDB (Data-/Program-write data bus, 32 бита – передает данные во время записи в программную память или в память данных).

Исключена одновременная запись и чтение в программную память (используется одна физическая шина адреса PAB); одновременная запись в программную память и в память данных (используется одна физическая шина данных DWDB). Параллельное выполнение остальных сочетаний операций возможно. Например, модуль CPU может одновременно инициировать чтение из программной памяти (PAB, PRDB), чтение из памяти данных (DRAB, DRDB) и запись в память данных (DWAB, DWDB).

Указанная система внутренних шин названа разработчиками Texas Instruments «модифицированная гарвардская архитектура». Главное ее достоинство – обеспечение параллельного выполнения сразу нескольких действий. В течение одного цикла возможна выборка команды, считывание данных и их запись. Кроме того, в течение одного цикла в АЛУ можно вводить два 32-битных операнда для последующего умножения.

Для сравнения, при вводе через внешний интерфейс минимально необходимо 4 цикла, т.к. внешняя ША имеет 19 бит, а внешняя ШД – 16 бит.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.