Структурная схема контроллера изображена на (рис.1). Устройство состоит из следующих основных блоков: модуль микропроцессора, модуль памяти, пульт оператора, модуль ввода-вывода аналоговых сигналов, модуль прерывания, модуль вывода импульсов. Модуль микропроцессора состоит из микропроцессора КР1821ВМ85А,регистры серии КР1533ИР33 и шинного формирователя КР1533АП6. Все структурные блоки микроконтроллера подключаются на общую шину данных. Модуль памяти выполняется на микросхемах постоянной (ПЗУ) и оперативной (ОЗУ) памяти. ПЗУ предназначено для хранения программного обеспечения микроконтроллера и данных для начальной инициализации, в ОЗУ располагаются текущие данные программы. Микропроцессор КР1821ВМ85А имеется встроенный программируемый контроллер прерывания (ПКП). Она позволяет осуществлять прерывания основной программы микропроцессора по одному из четырех запросов прерывания.

МК с требуемой периодичностью вырабатывает управляющие сигналы на своих выходных портах в соответствии с законом управления. Некоторая часть управляющих сигналов интерпретируется как совокупность простых двоичных сигналов управления, которые через схемы формирователей сигналов (усилители мощности, реле, оптроны и т.п.) поступают на исполнительные устройства. Другая часть управляющих сигналов представляет собой многоразрядные двоичные коды, которые через цифро-аналоговые преобразователи (ЦАП) воздействуют на исполнительные устройства аналогового типа. С помощью пульта управления (ПУ) оператор получает возможность управлять работой МПС: запускать ее и останавливать, выдавать значение некоторых сигналов, снимать с индикаторов информацию о состоянии объекта и т.п.

Основные используемые микросхемы:

Микропроцессор – КР1821ВМ85А;

ОЗУ – КР537РУ8;

ПЗУ – КР556РТ14;

Порты ввода/вывода – КР580ВВ55А,регистры серии КР1533

АЦП – К1108ПВ1(8 – разрядов);

ЦАП – К1108ПА1.

2.1 Модуль процессора

Модуль процессора представленный на (рис.2) состоит из процессора КР1821ВМ85 (DD2), логических элементов (DD3, DD5) формирующих сигналы управления, регистров (DD7, DD8) формирующих шину адреса и двунаправленный шинный формирователь (DD6) формирующий шину данных.

Рис.2 Модуль процессора

Назначение и характеристика элементов составляющих модуль.Микропроцессор КР1821ВМ85 изображен на (рис.3)

DIP – технология

Характеристики:

1. работает при одном напряжении, питания +5В;

2. имеет внутренний тактов генератор, внутренняя. такт. частота 0,5 – 3 мГц;

3. удобная система прерывания;

4. отрабатывает сигнал управления системой;

5. имеет возможность последовательного ввода и вывода данных;

6. имеет такую же систему команд, как и ВМ80, но добавлены 2 команды.

Назначение выводов :

X1, X2 – выводы для присоед. времязадающей цепочки ( кварцевый генератор );

![]() – вход сигн. нач. установки;

– вход сигн. нач. установки;

RESOUT - выход сигн. нач. установки;

READY – вход сигн. готовности;

SID – вход последов. данных;

SOD – выход посл. данных;

|

TRAP |

} |

|

|

RST 7.5 |

||

|

RST 6.5 |

Входы запросов прерываний |

|

|

RST 5.5 |

||

|

INTR |

HOLD – вход запроса захвата;

AD0…AD7 – совмещённые линии данных и мл. байтва адреса;

|

UCC |

} |

+5B входы питания |

|

GND |

0B |

CLK – выход сигн. тактов частоты;

|

S0 |

} |

сигналы состояния МП. |

|

S1 |

I0 / M – сигн. обращения к портам или к памяти:

если I0 / M = 1 – к портам;

I0 / M = 0 – к памяти.

ALE – разрешение фиксации адреса;

|

|

} |

стробы записи чтения |

|

|

![]() – строб подтверждения прерывания.

– строб подтверждения прерывания.

Рис.3 Процессор КР1821ВМ85

Таблица 1 Система прерываний МП ВМ85

|

Наименование вывода |

Приоритет |

Адрес перехода при прерывании (адрес ISR) |

Активный сигнал для выбора |

|

TRAP |

1 |

0024 H |

Перепад (0®1) или высокий уровень |

|

RST 7.5 |

2 |

003C H |

Перепад (0®1) |

|

RST 6.5 |

3 |

0034 H |

Высокий уровень |

|

RST 5.5 |

4 |

002C H |

|

|

INTR |

5 |

согласно коду RST N |

|

Все запросы прерываний принято делить на 2 вида:

– маскируемые;

– немаскируемые.

Маскируемые называется запрос, который можно программно запрет или разрешение. Если прерывание невозможно запретить программно оно называется немаскируемым.

TRAP – вход запроса немаскируемого прерывания. Остальные прерывания называются маскируемыми.Немаскируемые прерывания используются для реакции МП на аварийные ситуации.

Данный процессор имеет в своём составе встроенный генератор, что даёт возможность обходиться без внешних тактовых импульсов. Для обеспечения работы внутреннего тактового генератора необходима лишь времязадающая цепь. Она может быть построена как с использованием кварцевой стабилизации, так и без неё. В данном модуле установлен кварцевый резонатор на частоту Fрез=2Fт, а также ёмкость С1 =20 pF. МП имеет выход SYNC, с которого выходят тактовые импульсы обеспечивающие синхронизацию всей МП системы. Цепь R1, C1 выполняет начальную установку МП при включении питания. Обычно R1=10 кОм, С1=1 мкФ. С вывода SRO снимается сигнал для начальной установки (сброса) различных устройств МПС. Выводы TRAP, RST7.5, RST6.5, RST5.5 и INTR – это входы запросов прерывания. Т.к выход INTR не используется, на вход подан низкий логический уровень.

Микросхемы логических элементов (DD3, DD5).Данные микросхемы выбраны из серии KР1533. Они преобразуют сигналы управления МП ![]() ,

,

![]() ,

, ![]() в

системные сигналы управления

в

системные сигналы управления ![]() ,

, ![]() ,

, ![]() ,

,

![]() .

.

Сигналы управления имеют следующее назначение:

![]() – чтение из

памяти;

– чтение из

памяти;

![]() – запись в

память;

– запись в

память;

![]() – чтение

из порта;

– чтение

из порта;

![]() – запись

в порт.

– запись

в порт.

Микросхемы регистров (DD7, DD8).Т.к нагрузочная способность выходов МП мала (одна ТТЛ нагрузка) то для обеспечения работы процессора на шину адреса необходимо устанавливать буферные элементы. Другая причина установки регистров заключается в том, что шина данных и младшие 8 разрядов ША объединены в единую магистраль. В качестве регистров используются ИМС КР1533ИР33.

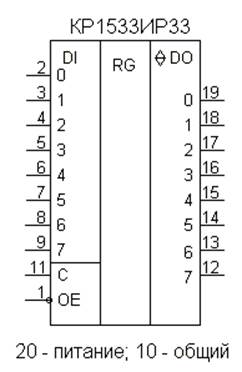

Микросхема КР1533ИР33 представляет собой восьмиразрядный буферный регистр. Условное обозначение приведено на (рис.4) . Данный регистр построен на

D–триггерах, имеет восемь входов данных D0...D7 и восемь выходов Q0...Q7. Выходные буферные элементы регистра имеют третье z– состояние, которое наступает, если на вход ЕОподать напряжение высокого уровня. Все триггеры имеют общий тактовый вход С(вход стробирования). Микросхема имеет ТТЛ уровни.

Назначение выводов:

9–2 – (D7–D0) – входные данные;

19–12 – (Q7–Q0) – выходные данные;

11 – (C) вход стробирования;

20 – (+U) напряжение источника питания;

10 – (GND) общая земля;

Основные электрические параметры:

Выходное напряжение ![]() ,В………………..0.4;

,В………………..0.4;

Выходное напряжение ![]() ,В………………...2.4;

,В………………...2.4;

Входной ток ![]()

![]() ,мА………………………….–0.4;

,мА………………………….–0.4;

Входной ток ![]() ,мА………………………….0.02;

,мА………………………….0.02;

![]()

Потребляемый ток Iпот.,мА…………………….40;

Напряжения питания +U,В……………………..5;

Рис.4 УГО и цоколёвка МС КР1533ИР33

Микросхема шинного формирователя (DD6).Для формирования шины данных используется специализированный шинный

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.