операции приёма регистры I2CxRSR и I2CxRCV создают двойной буфер приёмника. Это позволяет принимать следующий байт данных до того как был прочитан предыдущий.

Если модуль получает второй байт прежде чем в программе будет прочитан предыдущий байт из регистра I2CxRCV, то происходит переполнения приёмника и устанавливается бит I2COV (I2CxSTAT <6>). Байт, что был в регистре I2CxRSR теряется. Дальнейший прием и тактирование блокируется покудова модуль не увидит на шине состояние Start/Repeated, Start/Stop. Если флаг I2COV был сброшен, то приём может продолжаться обычным образом. Если флаг I2COV не очищен, модуль получит следующий байт правильно, но пошлет NACK. Тогда будет невозможно получить следующие байты или затянуть такты, пока не будет обнаружено условие Start/Repeated, Start/Stop.

Регистр I2CxADD содержит адрес ведомого устройства. В режиме с 10-ти битовой адресацией все биты разрешены. В режиме с 7-ми битовой адресацией, только биты <6:0> I2CxADD разрешены. Обратите внимание, что биты <6:0> I2CxADD соответствуют верхним семи битам в байте адреса; бит Read/Write не включен в этот регистр. Бит A10M (I2CxCON <10>) определяет ожидаемый режим адресации ведомого. Используя регистр I2CxMSK с регистром I2CxADD в режиме адресации ведомого, одна или более разрядных позиций может быть удалена из точного соответствия адреса, разрешая модулю в режиме ведомого ответить на множественный адресный запрос.

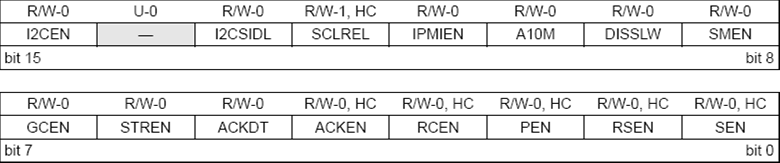

I2CxCON регистр управления

бит 15I2CEN: бит включения I2Cx

1 = активизирует модуль I2Cx и конфигурирует выводы SDAx и SCLx для работы с I2C

0 = отключает модуль I2Cx; все выводы I2C управляются как порты ввода/вывода бит 14Нереализованный: Читается как ‘0’

бит 13I2CSIDL: Останавливаться ли в Idle режиме

1 = прекратить работу модуля, когда устройство входит в Idle режим

0 = продолжать работу модуля в Idle режиме бит 12SCLREL: Бит управления отпусканием SCLx (при работе как ведомый I2C)

1 = Освободить тактовую линию SCLx

0 = Удерживать SCLX низким уровнем (такт затягивается)

Если STREN = 1:

Бит - R/W (то есть, программное обеспечение может запись '0', чтобы инициализировать задержку и записать '1', чтобы освободить тактовую линию). Аппаратно сбрасывает в начале передачи ведомым и в конце приёма ведомым.

Если STREN = 0:

Бит - R/S (то есть, программное обеспечение может только запись '1', чтобы отпустить тактовую линию). Аппаратные средства сбрасывает в начале передачи ведомым.

бит 11IPMIEN: бит включения Intelligent Platform Management Interface (IPMI)

1 = IPMI поддержка режима разрешена; признаются все адреса

0 = IPMI поддержка режима отключена бит 10A10M: Обращение к ведомому по 10-ти битному адресу

1 = регистр I2CxADD – адрес ведомого из 10-ти бит

0 = регистр I2CxADD – адрес ведомого из 7-ми бит бит 9DISSLW: Отключите Служебный бит Скорости просмотра файла изображения

1 = заблокированный контроль{управление} скорости просмотра файла изображения

0 = контроль{Управление} скорости просмотра файла изображения позволил бит 8SMEN: SMBus Input Levels bit

1 = Enable I/O pin thresholds compliant with SMBus specification

0 = Disable SMBus input thresholds

бит 7GCEN: Разрешает общий вызов (в режиме ведомого I2C)

1 = разрешает прерывание, когда получен общий адрес запроса в регистр I2CxRSR (модуль разрешён для приёма)

0 = запрещёно общий адрес зароса бит 6STREN: Задержка тактов SCLx (Только режим ведомого I2C; используемый вместе с битом SCLREL)

1 = Разрешить программному обеспечению или приёмнику затягивать тактовые импульсы

0 = Запретить программному обеспечению или приёмнику затягивать

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.