DMA для dsPIC

1. ВВЕДЕНИЕ

Контроллер Прямого доступа к памяти (DMA) - важная подсистема. Эта подсистема облегчает передачу данных между CPU и периферийными устройством без помощи CPU. dsPIC33F контроллер DMA оптимизирован для высокоэффективных, внедренных приложений реального времени, где детерминизм и системное время ожидания имеют высокое значение.

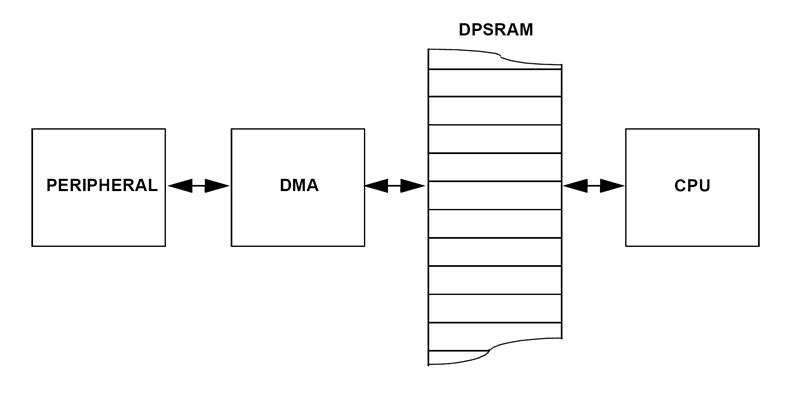

Контроллер DMA передает данные между периферийными регистрами данных и пространством данных SRAM. dsPIC33F подсистема DMA использует двухпортовую SRAM память (DPSRAM) и структуру регистров, которые позволяют DMA работать с помощью его собственных независимых шин адреса и данных без взаимодействия с CPU. Эта архитектура устраняет потребность выделении программных циклов, которые замедляют CPU, когда требуется более высокая приоритетная передача DMA. И CPU и контроллер DMA могут записать и читать в\из адресов в пределах пространства данных без вмешательства CPU. Альтернативно, на операции DMA и передачу данных в\из памяти и периферийных устройств не воздействует обработка CPU. Например, когда Самопрограммирующаяся операция Во время выполнения (RTSP) выполняется, CPU не выполняет никаких команд, пока RTSP не закончится. Это условие, однако, не воздействует на передачу данных в\из памяти и периферийных устройств.

Рисунок 1. DMA контроллер

DMA контроллер поддерживает 8 независимых каналов.

Каждый канал может быть конфигурирован для передач в или из выбранных периферийных устройств. Периферийные устройства, поддерживаемые контроллером DMA включают:

• ECAN

• Интерфейс Конвертера Данных (DCI)

• 10-bit/12-bit Аналого-цифровой Конвертер (ADC)

• Последовательный Периферийный Интерфейс (SPI)

• UART

• Input Capture

• Output Compare

Кроме того, передачи DMA могут быть вызваны Таймерами а так же внешними прерываниями.

Каждый канал DMA однонаправлен. Два канала DMA должны быть распределены, чтобы читать и записывать в периферийное устройство. Если больше чем один канал получает запрос на передачу данных, то приоритеты распределяются согласно номеру канала. Каждый канал DMA перемещает блок до 1024 элементов данных, после которого он генерирует прерывание CPU, чтобы указать, что блок доступен для обработки.

Контроллер DMA обеспечивает следующие функциональные возможности:

• Восемь каналов DMA

• Режим косвенной Регистровой адресации с Постприращением

• Режим косвенной Регистровой адресации без Постприращения

•Режим Периферийной Косвенный адресации (периферийное устройство генерирует адрес назначения)

• прерывание CPU после половины или полного окончания пересылки блока

• передачи Байтами или словами

• Фиксированный арбитраж приоритетов каналов

• Ручное (программное) или Автоматическое (периферия запрашивает DMA) инициирование передач

• режимы Однократной или Автоповторной пересылки блока

• режим Ping-Pong (автоматический переключение между двумя стартовыми адресами DPSRAM после окончания каждой пересылки блока)

• запрос DMA для каждого канала может быть выбран из любого поддерживаемого источника прерывания

• особенность поддержки Отладки

2 DMA РЕГИСТРЫ

Каждый канал DMA имеет набор из шести регистров управления и состояний.

•DMAxCON: Регистр Управления Канала DMA x

Этот регистр конфигурирует соответствующий канал DMA, допускают/отключают канал, определяет размер передачи данных, направление и метод блокового прерывания, выбирает Способ адресации Канала DMA, Operating режим и режим Null Data Write.

•DMAxREQ: Регистр Выбора IRQ Канала DMA x

Этот регистр связывает канал DMA с определенным DMA-способным периферийным устройством, назначая IRQ периферийного устройства на канал DMA.

•DMAxSTA: Регистр Смещения Адреса Начала A DPSRAM Канала DMA x

Этот регистр определяет смещение начала первого адреса от базового адреса DMA DPSRAM блока данных, который будет передан каналом DMA x к или от DPSRAM.

Чтение этого регистра возвращают значение последнего смещения адреса передачи DPSRAM. Запись в этот регистр, в то время как канал x разрешен (то есть, активный) может привести к непредсказуемому поведению и ее нужно избегать.

•DMAxSTB: Регистр Смещения Адреса Начала B DPSRAM Канала DMA x

Этот регистр определяет смещение начала второго адреса от базового адреса DMA DPSRAM блока данных, который будет передан каналом DMA x к или от DPSRAM.

Чтение этого регистра возвращают значение последнего смещения адреса передачи DPSRAM. Запись в этот регистр, в то время как канал x разрешен (то есть, активный) может привести к непредсказуемому поведению и ее нужно избегать.

•DMAxPAD: Регистр адреса Периферии Канала DMA x

Этот регистр для записи-чтения содержит статический адрес периферийного регистра данных запись в этот регистр, в то время как соответствующий канал DMA разрешен (то есть, активный) может привести к непредсказуемому поведению и ее нужно избегать.

•DMAxCNT: Регистр Счетчика Передачи Канала DMA x

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.