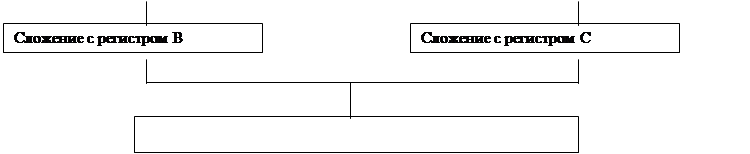

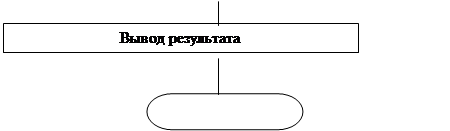

Алгоритм функционирования микропроцессорного устройства приведен на рис.1. В данном алгоритме осуществляются следующие действия. Сначала необходимо обнулить регистры B и C затем запомнить число каналов N и адрес начальной ячейки памяти. Далее создадим цикл опроса входных каналов. В нем осуществляется выбор канала, пересылка данных в память и уменьшение номера канала N. Выход из цикла осуществляется при N=0. Дальше происходит обработка данных в соответствии с заданием. Запоминается число каналов N, начальный адрес памяти. В аккумулятор записывается содержимое ячейки памяти с начальным адресом, далее к содержимому аккумулятора прибавляется единица и проверяем есть ли перенос, если перенос присутствует, то вызванное заново данное суммируем с регистром С. В регистре В будем хранить сумму из четных данных, в С – нечетные. После перебора всех данных на выход микропроцессорной системы выдается минимальное и максимальное значение среди входных сигналов.

Начало

|

Загрузка в рег. D кол-ва каналов

|

Загрузка в рег.пару HL начального адреса памяти

|

Вывод адреса каналов на коммутатор каналов

|

Ввод сигнала в аккумулятор

![]() Запись

аккумулятора в память

Запись

аккумулятора в память

![]() Увеличение

адреса памяти на 1

Увеличение

адреса памяти на 1

|

Уменьшение регистра D на 1

нет

нет

![]() D=0

D=0

![]() да

да

Загрузка в рег. D кол-ва каналов

|

|||

![]() Загрузка в

рег.пару HL начального адреса памяти

Загрузка в

рег.пару HL начального адреса памяти

|

Загрузка аккумулятора из памяти

![]()

![]()

Сложение со вторым байтом

|

А

|

А

![]()

![]()

![]()

![]() А=нечет

А=нечет

|

|

|

|||

|

|||

Увеличение адреса памяти на 1

![]()

![]() Уменьшение

регистра D на 1

Уменьшение

регистра D на 1

![]()

нет

нет

![]()

![]() D=0

D=0

да

да

|

![]() Пересылка из

С в А

Пересылка из

С в А

|

Конец

Распределение адресного пространства.

0000

0000

ПЗУ

003F

![]() 0040

0040

ОЗУ

Рабочая программа устройства.

При разработке программы сбора и обработки данных будем использовать регистровую пару HL для адресации области памяти. В качестве счетчика каналов будем использовать регистр D. Счет каналов организуем в обратном порядке, потому что не принципиально в каком порядке их опрашивать, но такой вариант позволяет повысить быстродействие системы, т.к. из каждого цикла исключается операция сравнения.

Метка |

Мнемокод |

Операнды |

Комментарий |

K4:K1:K2: K3: |

LXI MVI LXI OUT IN MOV DCR INX JNZ MVI LXI MOV ADD JC MOV ADD JMP MOV ADD INX DCR JNZ MOV OUT MOV OUT JMP |

B, 0000 D, 00001000 H, 0040 00 01 M, A D H K1 D, 00001000 H, 0040 А, M 00000001 K1 A, M B K3 A, M C H D K2 A, B 02 A, C 02 K4 |

Обнуление регистров В и С Загрузка регистра D Загрузка начального адреса ОЗУ Вывод адреса канала на коммутатор Ввод данных с мультиплексора Запись данных в память Декремент регистра D Инкремент регистровой пары HL Проверка условия выхода из цикла опроса каналов Загрузка регистра D Загрузка начального адреса ОЗУ Загрузка аккумулятора из памяти Сложение со вуторым байтом Проверка условия нечетности Загрузка аккумулятора из памяти Сложение с регистром B Безусловный переход Загрузка аккумулятора из памяти Сложение с регистром С Инкремент регистровой пары HL Декремент регистра D Проверка условия выхода из цикла сравнения данных Пересылка из B в A Вывод результата Пересылка из C в A Вывод результата Повтор программы |

Таблица размещения программы в ПЗУ.

|

Адрес памяти |

Метка |

Мнемокод |

|

0000 0001 0002 0003 0004 0005 0006 0007 0008 0009 000A 000B 000C 000D 000E 000F 0010 0011 0012 0013 0014 0015 0016 0017 0018 0019 001A 001B 001C 001D 001E 001F 0020 0021 0022 0023 0024 0025 0026 0027 0028 0029 002A 002B 002C 002D 002E 002F 0030 0031 0032 0033 0034 0035 |

K4 K1 K2 K3 |

LXI B 00 00 MVI D 00001000 LXI H 40 00 OUT 00 00 IN 01 00 MOV M A DCR D INX H JNZ 08 00 MVI D 00001000 LXI H 40 00 MOV A M ADD 00000001 JC 08 00 MOV A M ADD B JMP 26 00 MOV A M ADD C INX H DCR D JNZ 24 00 MOV A B OUT 02 00 MOV A C OUT 02 00 JMP 03 00 |

Оценку быстродействия будем осуществлять с использованием блок-схемы и с учетом длительности выполнения каждой команды (см. таблицу).

|

Команда |

Такты |

|

MVI LXI OUT IN MOV ADD INX JNZ DCR JC JMP |

7 10 10 10 5 4 5 10 5 10 10 |

Найдем количество тактов, необходимое для выполнения программы (с учетом циклов).N=10+7+10+(10+10+5+5+5+10)*8+7+10+(5+4+10+5+4+10+5+4+5+5+10)*8+

+5+10+5+10+10=980 такта. Тактовая частота микропроцессора fт = 2,5 МГц. Период выполнения программы можно рассчитать следующим образом T = N*tи , где tи = 1/fт .

T = 980/2.5*106 = 0,392 мс. Такое достаточно низкое быстродействие объясняется большим числом каналов. Повысить его можно, если не записывать в память данные, а производить обработку в реальном масштабе времени.

Приложение.

Цены на составляющие устройства сбора и обработки данных.

|

Наименование |

Цена, р. |

|

Центральный процессор КР580ВМ80 Генератор тактовых импульсов КР580ГФ24 Системный контроллер КР580ВК28 Буферный регистр КР580ИР82 Устройство ввода вывода КР 580 ВВ 55 Оперативное запоминающее устройство КР537РУ5 Постоянное запоминающее устройство К537РФ1 Мультиплексор К155КП5 АЦП К531КП2 Итог |

12 3 3,5 3 15 1 10 0,8 30 82,1 |

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.