Для передачи одного слова МП должен выполнить несколько команд среди этих команд есть и вспомогательные. Изменение адреса памяти , изменение и анализ содержимого программного счетчика и счетчика слов . В некоторых МП невозможно в одной команде передавать данные из внешнего устройства в память сначала необходимо данные принять процессором , а затем из процессора передать в память. Когда требуется передавать большие массивы информации, то МП выступает в роли лишнего звена т.к. транзитом пропускает через себя информацию. Память микро ЭВМ позволяет выполнять чтение, запись данных со скоростью несколько мегабайт в секунду, поэтому в режиме прямого доступа к памяти процессор отключается и не участвует в операции ввода вывода. Контроллер ПДП в случае необходимости обмена сообщает процессору сигналом запрос на захват шины, процессор отвечает сигналом подтверждения захвата. С этого момента контроллер получает шину в свое распоряжение. Режим ПДП позволяет получить максимальные возможности скорости обмена. Программы обмена в этом случае нет, обмен осуществляется аппаратно, данные передаются напрямую.

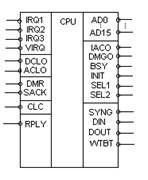

33.К1801ВМ1

Двоичный 16-разрядный процессор с внутренним блоком микропрограммного управления имеющий 8 регистров общего назначения , 4 уровня запроса прерываний. Объем адресуемой памяти 64 кб. Имеет следующие режимы адресации: регистровая, регистровая косвенная, автоинкрементная, автоинкрементная косвенная, автодекрементная, автодекрементная косвенная, индексная, индексная косвенная.

AD0-AD15- совмещенная шина адреса и данных

IAKO-

Предоставление прерывания

IAKO-

Предоставление прерывания

DMGO- разрешение прямого доступа

BSY-занятость канала

INIT-установка

SEL1, SEL2- выборка регистров ввода-вывода

SYNG-обмен

DIN-чтение данных

DOUT-запись данных

WTBT-запись байт

CLC-сигнал синхронизации

RPLY- ответ

SACK- подтверждение выборки

DMR-требование прямого доступа

ACLO-авария сетевого питания

DCLO-авария источника питания

VIRQ-требование прерываний

IRQ1-3-запросы внешних прерываний

Операционный блок выполняет арифметические и логические операции, формирует адреса выполняемых команд, хранит промежуточные результаты . Управление работой блока МП осуществляется блоком микро программного упровления.

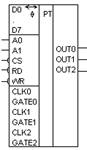

34. Программируемый таймер .УГО. Назначение выводов. Основные блоки.

МС КР 580ВИ53 предназначена для задания временных

интервалов и времени функций микропроцессорных систем.

МС КР 580ВИ53 предназначена для задания временных

интервалов и времени функций микропроцессорных систем.

D0-D7-входы данных.

А0-А1-адресные линии.

CS-выбор кристалла.

RD- строб чтения.

WR-строб записи.

CLK0-CLK2-счетный вход.

OUT0-OUT2-выходы.

GATE0-GATE2-если равно 1 то счет разрешён.

Счетчик может работать в шести режимах.

Программирование таймера зак-ся в записи регистра управляющего слова. Для доступа к каждому счетчика А0-А1 необходимо подавать комбинации нулей и единиц.

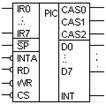

35. Контроллер приоритета прерываний. УГО. Назначение выводов. Основные блоки Позволяет обслуживать до 8 запросов прерываний. БИС решает задачи:

определение запроса и в случае разрешения

прерываний передачу управления

на соответствующую подпрограмму

обслуживания. МС

определение запроса и в случае разрешения

прерываний передачу управления

на соответствующую подпрограмму

обслуживания. МС

позволяет программно задавать различные режимы приоритетов, разрешать или запрещать отдельные запросы.

IR0-IR7

–запросы прерываний

от устр-ва

ввода.

IR0-IR7

–запросы прерываний

от устр-ва

ввода.

SP - +5 В

INTA- строб подтверждения

прерываний.

RD – строб чтения,

WR – строб записи

CS- вывод

Кристалла

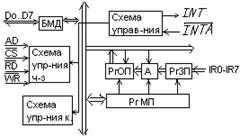

БИС: Схема управления контролирует процесс обработки запросов:

- регистр запросов (Рг3П) – формируются все текущие запросы.

- адаптер (А) – определяет среди текущих запросов прерывания запрос с макс. приоритетом.

- регистр маски прерывания (Рг МП) – позволяет запрещать обработку отдельных запросов.

- схема управления каскадированием – служит для организации взаимодействия ведущего и ведомого контроллеров.

- схема управления чтением-записью.

- буфер магистрали данных(БМД) – служит для развязки внутренней и внешней магистрали.

При реализации контроллера прерываний можно использовать в зав-ти от необходимого числа запросов одну или несколько МС. Число ведомых БИС ограничено кол-вом свободных входов запросов у основного контроллера.

36. Контроллер прямого доступа к памяти. УГО. Назначение выводов. Основные блоки.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.