Лекция №15 (3.11.06)

Примеры использования данной структуры.

1012

x-mp/48

1011

Данная система использует жидкостное охлаждение.

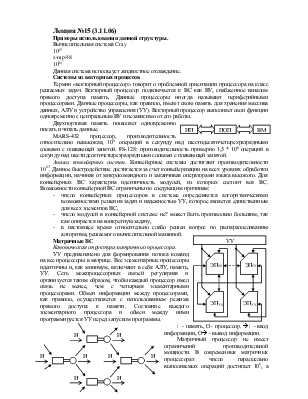

![]() Термин «векторный процессор»

говорит о проблемной ориентации процессора на класс решаемых задач. Векторный

процессор подключается к ВС как ВУ, снабженное каналом прямого доступа память.

Данные процессоры иногда называют периферийными процессорами. Данные

процессоры, как правило, имеют свою память для хранения массива данных, АЛУ и

устройство управления (УУ). Векторный процессор выполняет свои функции

одновременно с центральным ВУ и независимо от его работы.

Термин «векторный процессор»

говорит о проблемной ориентации процессора на класс решаемых задач. Векторный

процессор подключается к ВС как ВУ, снабженное каналом прямого доступа память.

Данные процессоры иногда называют периферийными процессорами. Данные

процессоры, как правило, имеют свою память для хранения массива данных, АЛУ и

устройство управления (УУ). Векторный процессор выполняет свои функции

одновременно с центральным ВУ и независимо от его работы.

Двухпортовая память позволяет одновременно писать и читать данные.

MARS-432 процессор, производительность относительно невысокая, 109 операций в секунду над шестидесятичетырехразрядными словами с плавающей запятой. FS-128: производительность примерно 1,5 * 108 операций в секунду над шестидесятичетырехразрядными словами с плавающей запятой.

Анализ конвейерных систем. Конвейерные системы достигают производительности 1012. Данное быстродействие достигается за счет конвейеризации на всех уровнях обработки информации, начиная от микрокомандного и заканчивая операторами языка высокого. Для конвейерных ВС характерна идентичность модулей, из которых состоит вся ВС. Возможности конвейерной ВС ограничены по следующим причинам:

- число конвейерных процессоров в системе определяются алгоритмическими возможностями решения задач и надежностью УУ, которое является единственным для всех элементов ВС,

- число модулей в конвейерной системе не? может быть произвольно большим, так как опирается на конкретную задачу,

-

в настоящее время относительно слабо решен вопрос по

распараллеливанию алгоритма, решаемого вычислительной машиной.

в настоящее время относительно слабо решен вопрос по

распараллеливанию алгоритма, решаемого вычислительной машиной.

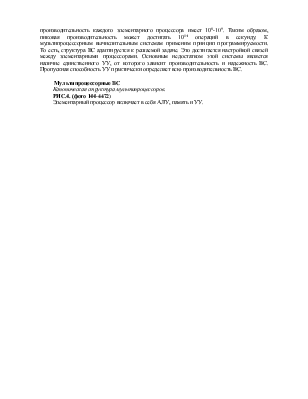

Матричные ВС

Каноническая структура матричного процессора.

УУ предназначено для формирования потока команд на все процессоры в матрице. Все элементарные процессоры идентичны и, как минимум, включают в себя АЛУ, память, УУ. Сеть межпроцессорных связей регулярная и организуется таким образом, чтобы каждый процессор имел связь не менее, чем с четырьмя элементарными процессорами. Обмен информации между процессорами, как правило, осуществляется с использованием режима прямого доступа к памяти. Состояние каждого элементарного процессора и обмен между ними программируется УУ перед запуском программы.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.