Задание: Спроектировать генератор exp(-kx2) биполярных периодических сигналов на базе 8-битных МП типа КР580ВМ80А/КР1821ВМ85 (Intel8080/85), Z80, М6800, М6802, М6809, или микро-ЭВМ серии К1816 (МК48 и МК51).

|

Исходные данные:

а) тактовая частота микропроцессора f = 2 МГц б) период следования T = 4 мс в) амплитуда сигнала U = 5В

г) длительность импульсов tи = 0,1*T

д) шаг квантования

- по времени, не более 50 мкс

- по амплитуде, не более 0,08 В

|

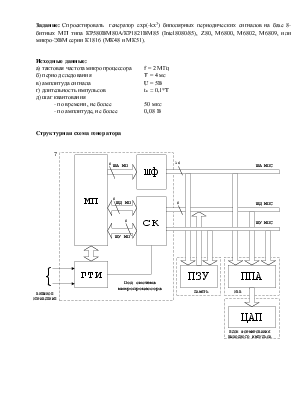

Генератор тактовых импульсов (ГТИ) предназначен для создания последовательности тактовых импульсов, синхронизирующих работу МПС, а также для формирования сигналов готовности сброса и строба состояния.

Информация, выдаваемая процессором на ШД и ША, может предназначаться большому числу устройств, подключенных к этим шинам (ПЗУ), а нагрузочная способность выводов МП обеспечивает подключение не более одной интегральной схемы ТТЛ, поэтому в ША и ШД включены буферы. Буфер МП построен на основе шинного формирователя (ШФ). Роль буферов ША и ШД выполняет системный контроллер, он также необходим для формирования сигналов управления для устройства памяти и ввода-вывода.

Устройство памяти, ПЗУ, предназначено для хранения управляющей программы. В качестве устройства ввода-вывода будем использовать программируемый адаптер параллельного интерфейса (ПАПИ или ППА, на схеме электрической принципиальной PPI). ПАПИ позволяет в данном случае переключать ШД МПС на работу с одним из своих портов. Он работает вместе с ЦАП.

Программируемый генератор сигналов выполнён на восьмиразрядномоднокристальном МП КР580 ВМ80А – это основной элемент МПК серии КР580.

Совместно с данным МП необходимо использовать генератор тактовых импульсов (ГТИ) из того же МПК-КР580 ГФ24 – он синхронизирует работу МП и в итоге, правильное функционирование МП (рис.) (CPU), ГТИ ГФ24 (G), а также системного контроллера (SC) КР580 ВК28 и двух буферных регистров (F) КР580 ВА86.

Генератор тактовых импульсов КР580 ГФ24 формирует высокоуровневые тактовые сигналы Ф1 и Ф2, не перекрывающиеся во времени, имеющие амплитуду до 12В и синхронизирующие работу процессора. Высокую стабильность ГТИ обеспечить можно путём подключения к выходим XTAL1 и XTAL2 кварцевого резонатора ZQ с резонансной частоты 18 МГц, что обеспечивает нормальное функционировании МП с тактовой частотой 1,6 МГц; сигнал STSTB- “строб состояние” формируется ГТИ при поступлении на его вход с процессора ВМ80 сигнала SYNC-“синхронизация”, свидетельствующего о начале машинного цикла, и поступающего на системный контроллер ВК28, где фиксируется состояние шины данных процессора. Сигнал RESIN- “установка по входу”, а именно при его поступлении, ГТИ формирует сигнал “RESET- установка”- он синхронизован с тактовым сигналом Ф2 и по нему осуществляется установка в исходное состояние компонентов микропроцессорного устройства. Системный контроллер КР580ВК28 (далее просто ВК28) выполняет роль буфера шины данных и осуществляет формирование управляющих сигналов обращения к устройству памяти и ввода-вывода, а также обеспечивает приём/передачу восьмиразрядной информации между шиной данных процессора и системной шиной. Подключение ВК28 к ШД процессора осуществляется с помощью двунаправленных выводов ДВ0-ДВ7. Непосредственно МП может выдавать на контроллер следующие управляющие сигналы: HLDA- “подтверждение захвата”, DBIN- “приём”- коммутирует ШД на ввод и WR – “запись”, и в зависимости от состояние этих сигналов, контроллер ВК28 формирует сигнал INTA- подтверждение прерывания или сигналы чтения(запись) при обращении к памяти или устройствам ввода-вывода. Буферные каскады ША выполнены на восьмиразрядных шинных формирователях КР580ВА86, с высокой нагрузочной способностью. Режим работы ВА86 определяется управляющими сигналами ОЕ- “разрешение выхода” и Т- направление передачи (рис.), так, при поступлении на вход ОЕ сигнала высокого уровнях, выходы А и В переходят в состояние “Откл.”. При наличии на входе ОЕ сигнала низкого уровня направление передачи, информации полностью определяется сигналом Т: при подаче на вход Т сигнала высокого уровня, передача данных осуществляется с канала А в канал В, при подаче на вход Т сигнала низкого уровня осуществляется обратная передача, т.е. в схеме необходимо “подвесить” вход Т- на нём будет, таким образом, состояние логической “1” всегда, что обеспечит прямую передачу с шины А (А0-А7) на шину В(В0-В7).

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.