Владимирский Государственный Университет

Кафедра конструирования и технологии радиоэлектронных средств

Отчет по лабораторной работе №4

по дисциплине ИТПРЭС

Работу выполнил: студент гр. Р-106

Работу принял: доц.

Владимир 2010

Задание на лабораторную работу.

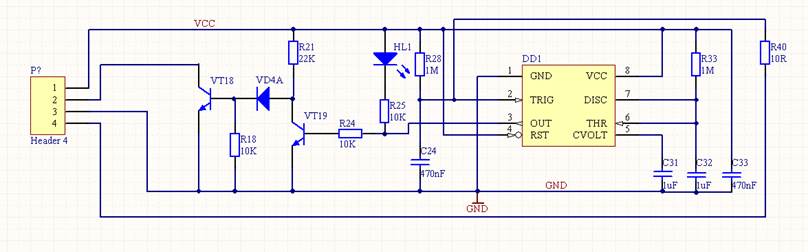

Сформировать электрическую схему (часть схемы курсового проекта).

Выполнить логическое моделирование (анализ переходных процессов).

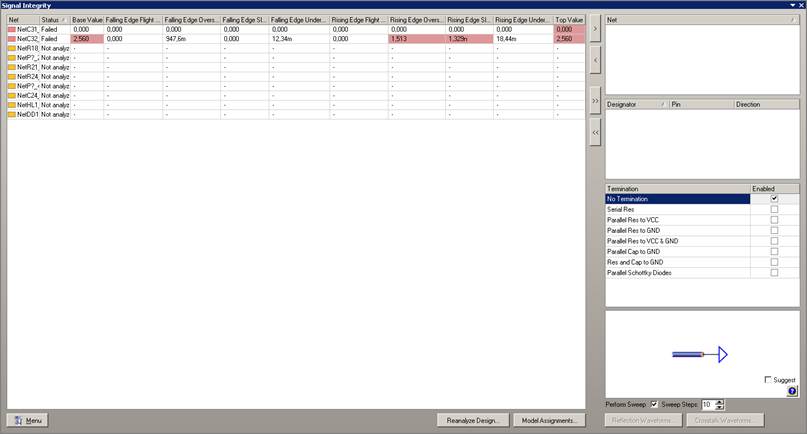

Выполнить посттопологический анализ целостности сигналов

Протокол работы.

Часть схемы курсового проекта выбранная для анализа.

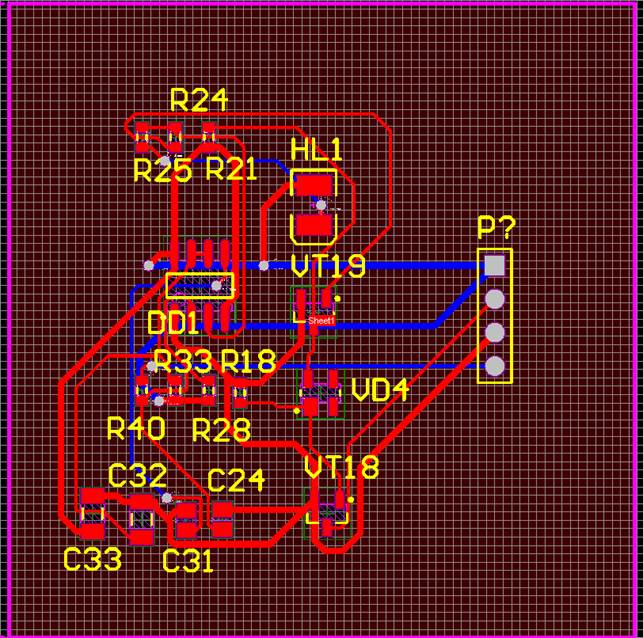

Трассировка проекта :

Посттопологический анализ проекта :

Возникшие ошибки и их решения:

Причина: отсутствие у элемента логической модели.

Решение: выбор элементов с наличием логическим описанием в своей библиотеке.

Так как для элемента NE555 не было найдено логического описания, то нет возможности выполнить предтопологическое моделирование.

Документы, полученные в ходе выполнения лабораторной работы.

Список цепей схемы в формате spice

PCB_Project1

*SPICE Netlist generated by Advanced Sim server on 10.06.2010 0:52:02

*Schematic Netlist:

V5Vpos Net5Vpos_1 0 +5

C24 0 NetC24_2 470nF CAP

C31 0 NetC31_2 1uF CAP

C32 0 NetC32_2 1uF CAP

C33 0 Net5Vpos_1 470nF CAP

DHL1 Net5Vpos_1 NetHL1_2 LED3

R18 0 NetR18_2 10K

R21 NetR21_1 Net5Vpos_1 22K

R24 NetDD1_3 NetR24_2 10K

R25 NetDD1_3 NetHL1_2 10K

R28 NetC24_2 Net5Vpos_1 1M

R33 NetC32_2 Net5Vpos_1 1M

R40 OUT NetC24_2 10R

XVD4A NetR21_1 NetR18_2 BAV23

QVT18 OUT2 NetR18_2 0 QBC846

QVT19 NetR21_1 NetR24_2 0 QBC846

.SAVE 0 Net5Vpos_1 NetC24_2 NetC31_2 NetC32_2 NetDD1_3 NetHL1_2 NetR18_2 NetR21_1

.SAVE NetR24_2 OUT OUT2 V5Vpos#branch @V5Vpos[z] @C24[i] @C31[i] @C32[i] @C33[i]

.SAVE @DHL1[id] @QVT18[ib] @QVT18[ic] @QVT18[ie] @QVT19[ib] @QVT19[ic] @QVT19[ie]

.SAVE @R18[i] @R21[i] @R24[i] @R25[i] @R28[i] @R33[i] @R40[i] @C24[p] @C31[p] @C32[p]

.SAVE @C33[p] @DHL1[p] @QVT18[p] @QVT19[p] @R18[p] @R21[p] @R24[p] @R25[p] @R28[p]

.SAVE @R33[p] @R40[p] @V5Vpos[p]

*PLOT AC -1 1 A=OUT A=OUT2

*Selected Circuit Analyses:

.AC LIN 100 1 1E6

*Models and Subcircuits:

.MODEL CAP C()

.MODEL LED3 D (IS=93.1P RS=42M N=7.47 BV=5 IBV=30U CJO=2.97P VJ=.75 M=.333

+ TT=4.32U)

.SUBCKT BAV23 10 30

D1 10 20 DIDEAL

D2 10 20 DRECOMB

D3 20 30 DHIGH

* Subcircuit models

.MODEL DIDEAL D ( IS = 3.7106E-09 N = 1.9403 TT = 3.751E-08 CJO = 7.9474E-13

+ VJ = 0.3905 M = 0.10536 BV = 319.86 IBV = 5.17E-06 )

.MODEL DHIGH D ( IS = 4.640134335 N = 1.9403 RS = 0.41967 )

.MODEL DRECOMB D ( IS = 9.61006E-09 N = 1.995636079 )

.ENDS BAV23

.MODEL QBC846 NPN( IS = 1.822E-14 NF = 0.9932 ISE = 2.894E-16 NE = 1.4 BF = 324.4

+ IKF = 0.109 VAF = 82 NR = 0.9931 ISC = 9.982E-12 NC = 1.763 BR = 8.29 IKR = 0.09

+ VAR = 17.9 RB = 10 IRB = 5E-06 RBM = 5 RE = 0.649 RC = 0.7014 XTB = 0 EG = 1.11

+ XTI = 3 CJE = 1.244E-11 VJE = 0.7579 MJE = 0.3656 TF = 4.908E-10 XTF = 9.51 VTF

+ = 2.927 ITF = 0.3131 PTF = 0 CJC = 3.347E-12 VJC = 0.5463 MJC = 0.391 XCJC =

+ 0.6193 TR = 9E-08 CJS = 0 VJS = 0.75 MJS = 0.333 FC = 0.979)

.END

Перечень элементов Bill Of Material

Comment Description Designator Footprint LibRef Quantity

"Cap Semi" "Capacitor (Semiconductor SIM Model)" "C24, C31" "CAPC2012L" "CapSemi" "2"

"Cap Semi" "Capacitor (Semiconductor SIM Model)" "C32, C33" "CAPC3216L" "CapSemi" "2"

"NE555D" "Precision Timer" "DD1" "D008_N" "NE555D" "1"

"LED3" "Typical BLUE SiC LED" "HL1" "DSO-C2/D5.6" "LED3" "1"

"Header 4" "Header, 4-Pin" "P?" "HDR1X4" "Header 4" "1"

"Res2" "Resistor" "R18, R21, R24, R25, R28, R33, R40" "RESC1608L" "Res2" "7"

"BAV23" "General-purpose Double Diode" "VD4" "SOT143_N" "BAV23" "1"

"BC846" "NPN General-purpose Transistor" "VT18, VT19" "SOT23_N" "BC846" "2"

Список параметров электрических цепей схемы NetList Status

|

GND |

Signal Layers Only |

91.3875mm |

|

NetC24_2 |

Signal Layers Only |

29.2428mm |

|

NetC31_2 |

Signal Layers Only |

31.8812mm |

|

NetC32_2 |

Signal Layers Only |

34.9649mm |

|

NetDD1_3 |

Signal Layers Only |

26.5074mm |

|

NetHL1_2 |

Signal Layers Only |

17.4502mm |

|

NetP?_2 |

Signal Layers Only |

23.2250mm |

|

NetP?_4 |

Signal Layers Only |

27.6856mm |

|

NetR18_2 |

Signal Layers Only |

13.4289mm |

|

NetR21_1 |

Signal Layers Only |

28.9343mm |

|

NetR24_2 |

Signal Layers Only |

40.3812mm |

|

VCC |

Signal Layers Only |

125.2781mm |

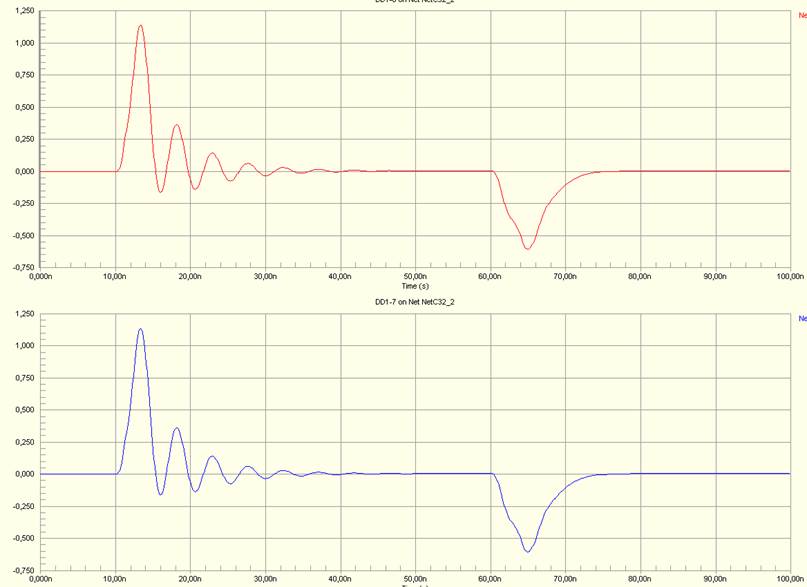

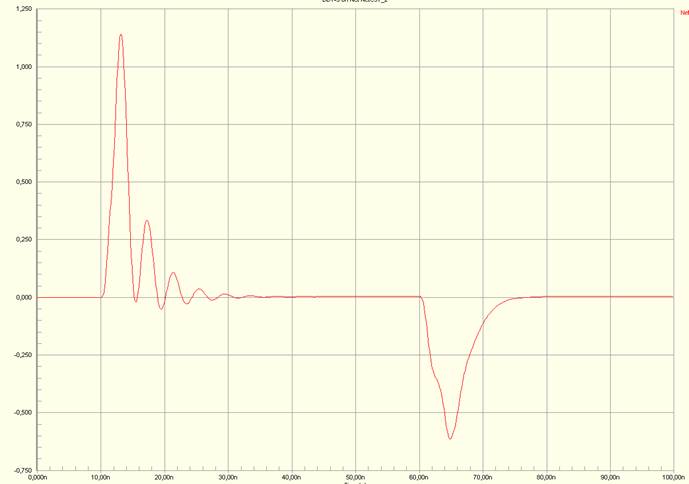

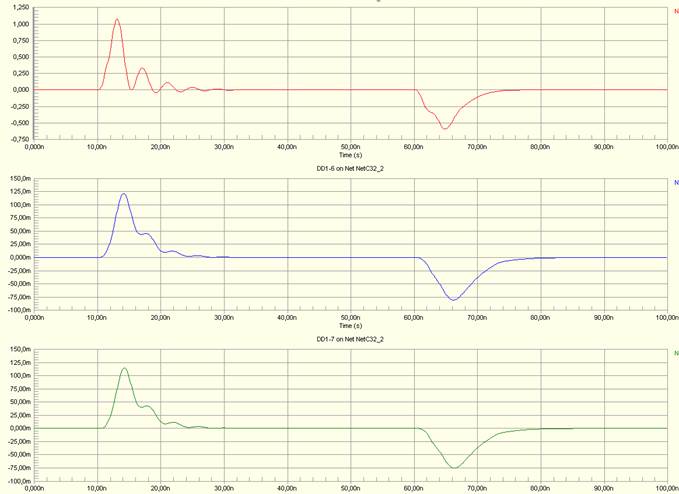

Результаты посттопологического анализа

Переотражение сигнала в проводнике NetC32_2

Переотражение сигнала в проводнике NetC31_2

Взаимные помехи межу проводниками NetC32_2 и NetC31_2

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.