· запустите временной анализатор и запишите матрицу задержек;

· с помощью временного анализатора определите Fmax - максимальную тактовую частоту работы счетчика;

· составьте тест для полной функциональной проверки счетчика.. Масштаб времени выберите, согласуясь с результатам временного анализа таким, чтобы не превысить максимальную тактовую частоту и чтобы легко определялось, какому набору входных сигналов соответствуют выходные сигналы счетчика. Выполните временное моделирование. Обратите внимание, синхронно ли изменяются все выходные сигналы счетчика. Проверьте работоспособность счетчика при тактовой частоте, превышающей Fmax;

· пользуясь редактором разводки или данными из файла отчета (Repot File) определите используемый ресурс СБИС ПЛ: число задействованных логических ячеек (макроячеек) и выводов;

· запишите логические выражения, синтезированные компилятором (раздел Equations в Repot File), объясните их.

5. Повторите действия по п.1, выполнив компиляцию в стандартном режиме Fast, и проведите исследования по программе п.2 при использовании той же ПЛИС.

6. Реализуйте счетчик на ПЛИС семейства MAX 7000. Установите заданную ПЛИС семейства MAX 7000 и выполните компиляцию проекта в стандартном режиме Fast

7. Сравните результаты реализации счетчика при различных режимах компиляции, типах СБИС ПЛ.

8.  Разработать

текстовый проект параметризированного делителя частоты. В качестве параметра

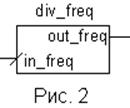

использовать коэффициент деления. Делитель должен иметь (рис. 2):

Разработать

текстовый проект параметризированного делителя частоты. В качестве параметра

использовать коэффициент деления. Делитель должен иметь (рис. 2):

· Вход тактовой частоты – in_freg.

· Выход тактовой частоты – out_freq.

· Длительность импульса выходного сигнала out_freq равна периоду сигнала in_freg.

· Выходной сигнал делителя частоты должен быть свободен от гонок.

· Коэффициент деления делителя по умолчанию установить равным 3.

9. Установите заданную ПЛИС семейства FLEX 10K и выполните компиляцию проекта в стандартном режиме Normal.

10. Создайте Include и Symbol файлы и скопируйте их вместе с файлом проекта div_freq.tdf в папку Lib для использования в лабораторной работе 4.

11. Проведите исследование делителя частоты:

· запустите временной анализатор и запишите матрицу задержек;

· с помощью временного анализатора определите Fmax - максимальную тактовую частоту работы делителя частоты;

· составьте тест для полной функциональной проверки делителя частоты. Масштаб времени выберите, согласуясь с результатам временного анализа таким, чтобы не превысить максимальную тактовую частоту и чтобы легко определялось, какому набору входных сигналов соответствуют выходные сигналы счетчика. Выполните временное моделирование. Обратите внимание, синхронно ли изменяется выходной сигнал делителя частоты. Проверьте работоспособность делителя частоты при тактовой частоте, превышающей Fmax;

· пользуясь редактором разводки или данными из файла отчета (Repot File) определите используемый ресурс СБИС ПЛ: число задействованных логических ячеек (макроячеек) и выводов;

12. Повторите действия по п.1, выполнив компиляцию в стандартном режиме Fast, и проведите исследования по программе п.2 при использовании той же ПЛИС.

13. Сравните результаты реализации делителя частоты при различных режимах компиляции, типах СБИС ПЛ.

Список рекомендуемой литературы

1. Антонов А.П. Язык описания цифровых устройств Altera AHDL. :Практический курс. -М., :Радио Софт, 2001 г. (с.8 – 148, с.194 - 200)

2. Стешенко В.Б. Плис фирмы ALTERA: проектирование устройств обработки сигналов -М., :ДОДЭКА, 2000.

3. Ашихмин А.С. Цифровая схемотехника. Современный подход. –М., :ТехБук, 2007. –288с. (с.230 - 283)

4. Комолов Д.А., Мяльк Р.А., Зобенко А.А., Филиппов А.С. Системы автоматизированного проектирования фирмы Altera MAX+plus II и Quartus II. Краткое описание и самоучитель. –М., ИП РадиоСофт, 2002 г. (с.19 – 188).

Контрольные вопросы

1. Основные этапы разработки проекта цифрового устройства на ПЛИС.

2. Создание и ввод текстового проекта. Назначение и особенности применения служебных операторов Title Statement, Options Statement, Define Statement и Function Prototype в текстовом проекте.

3. Структура описания текстового проекта. Назначение и содержание секций: Subdesign Section, Variable Section, Logic Section.

4. Объявление узлов (Node Declaration), объектов (Instance Declaration), регистров (Register Declaration) и цифровых автоматов (State Machine Declaration) в секции переменных (Variable Section). Особенности объявления примитив, мегафункций и LPM–функций.

5. Создание библиотеки собственных модулей и подключение ее к проекту. Создание файлов *.inc и *.sym для использования в иерархических проектах.

6. Способы программирования и конфигурирования ПЛИС (пассивные и активные; параллельные и последовательные; синхронные и асинхронные; JTAG). Защита ПЛИС от несанкционированного копирования.

7. Параметризированные и непараметризированные функции. Использование оператора Parameters Statement для создания параметризированных функций.

ЛАБОРАТОРНАЯ РАБОТА № 3

ПРОЕКТИРОВАНИЕ УЗЛОВ ЦОС

Цель работы: изучение функционирования и описания узлов ЦОС. Использование библиотечных функций для построения узлов ЦОС.

Программа работы

1. Ознакомьтесь с описанием параметризируемого модуля lpm_mult из состава библиотеки Megafunctions/LPM пакета Max+Plus II.

2. Разработать проект умножителя двух восьмиразрядных чисел со знаком без использования конвейера, используя модуль lpm_mult. Для создания проекта использовать мастер MegaWizard Plug-In Manager.

3. Выполните компиляцию проекта на ПЛИС семейства FLEX10K EPF10K20RC240-4. Определите используемые ресурсы СБИС ПЛ.

4. Проведите исследование умножителя:

· запустите временной анализатор и запишите матрицу задержек;

· с помощью временного анализатора определите Fmax - максимальную тактовую частоту работы умножителя;

· составьте тест для полной функциональной проверки умножителя. Масштаб времени выберите, согласуясь с результатам временного анализа таким, чтобы не превысить максимальную тактовую частоту и чтобы легко определялось, какому набору входных сигналов соответствуют выходные сигналы умножителя. Выполните временное моделирование. Обратите внимание, синхронно ли изменяются все выходные сигналы умножителя. Проверьте работоспособность умножителя при тактовой частоте, превышающей Fmax;

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.