0 0

1 1

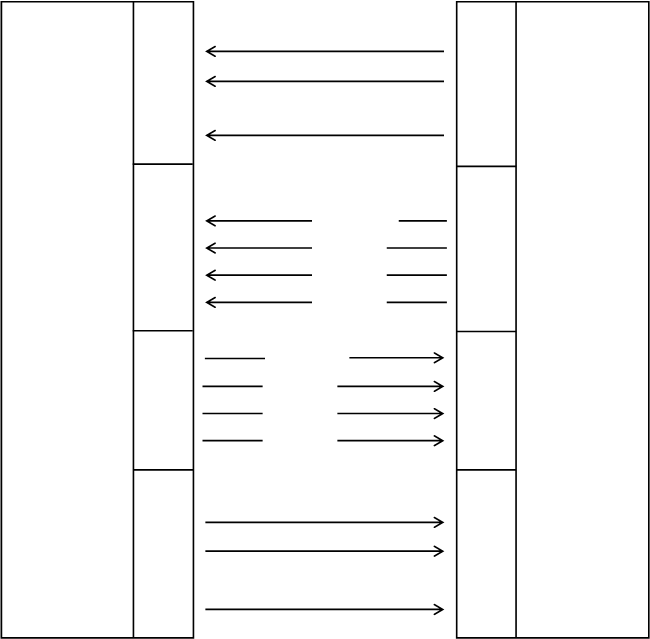

: Данные :

7 7

PC PC

0 СТР(2) 4

0 СТР(2) 4

1 ЗП(1) 5

2 ГИ(2) 6

3 ГП(1) 7

4 СТР(1) 0

5 ЗП(2) 1

6 ГИ(1) 2

7 ГП(2) 3

PA PB

0 0

1 1

: Данные :

7 7

Рис.3. Структура сопряжения ППА с источниками и

приемниками данных

В вычислительной технике принято называть программы, обеспечивающие обмен информацией микроЭВМ с различными ВУ, программами-драйверами. Каждому ВУ соответствует свой драйвер, и прикладная программа (программа пользователя) взаимодействует с ВУ посредством обращения к этим драйверам.

В соответствии с этой терминологией рассмотрим программу-драйвер ИРПР при использовании ППА в режиме 0. Драйвер обеспечивает выполнение функций инициализации, проверки готовности, ввода и вывода символа.

Примечание. Будем рассматривать драйвер ИРПР применительно к возможностям лабораторного макета, который обеспечивает одностороннюю связь между двумя микроЭВМ УМК. При этом один УМК является источником данных (сторона 1 на рис.3), а второй УМК является приемником данных (сторона 2 ).

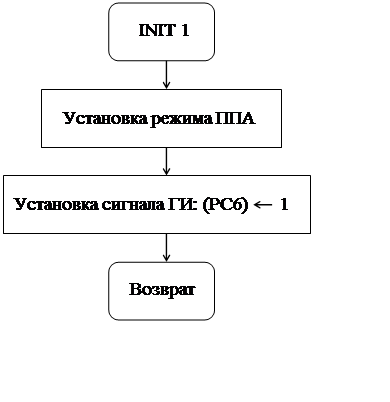

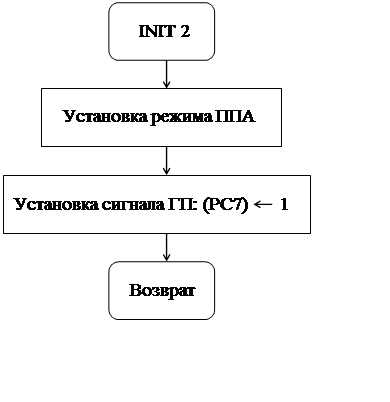

Драйвер состоит из шести подпрограмм, блок-схемы их алгоритмов приведены на рис. 4-9. Подпрограмма INIT1 производит инициализацию ППА и установку сигнала ГИ со стороны 1 путем занесения информации в регистр управляющего слова (РУС). При инициализации устанавливается режим 0 для всех портов, причем порт PB и младшая половина порта PC программируются на ввод, а порт PA и старшая половина порта PC - на вывод. Установка сигнала ГИ (разряд PC6) выполняется с помощью управляющего слова установки-сброса битов. Подпрограмма INIT2 производит инициализацию ППА и установку сигнала ГП (разряд PC7) со стороны 2.

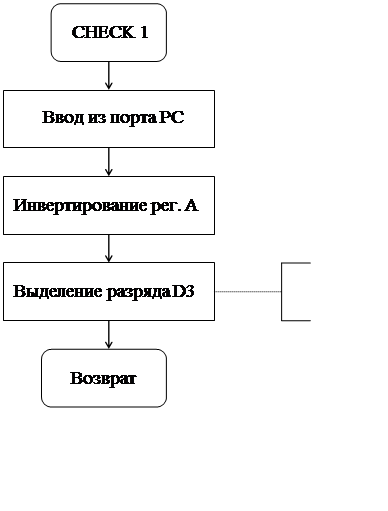

Подпрограмма CHECK1 проверяет готовность приемника (наличие сигнала ГП). При наличии этого сигнала в выходном параметре подпрограммы устанавливается признак готовности - флаг (Z)=1, при неготовности флаг (Z)=0.

Подпрограмма CHECK2 проверяет готовность источника (наличие сигнала ГИ). При наличии этого сигнала в выходном параметре подпрограммы устанавливается признак готовности - флаг (Z)=1, при неготовности флаг (Z)=0.

Подпрограмма OUTPUT1 осуществляет вывод данных (символа) из УМК со стороны 1 (выводимый символ предварительно размещается в регистре C). В начале подпрограммы в цикле ожидания контролируется появление единицы в разряде PC1. Эта единица интерпретируется как сигнал запроса ЗП от приемника. Далее выводится символ через порт PA адаптера и устанавливается сигнал СТР (единица в разряде PC4). После этого в цикле ожидания контролируется снятие сигнала ЗП со стороны приемника и, наконец, снимается сигнал СТР со стороны источника.

Подпрограмма INPUT2 осуществляет ввод символа в УМК стороны 2. В начале подпрограммы устанавливается сигнал запроса ЗП со стороны приемника (единица в разряде PC5) и проверяется наличие ответного сигнала СТР со стороны источника. Если этот сигнал установлен (разряд PC0=1), то осуществляется ввод символа из порта PB адаптера. Затем снимается сигнал ЗП со стороны приемника. Возврат из этой подпрограммы выполняется только после снятия сигнала СТР со стороны источника.

На основании рассмотренного драйвера ИРПР пользователь может разрабатывать различные программы для передачи данных - отдельных символов, массивов данных и т.д.

|

|||

|

|||

Рис.4. Блок-схема алгоритма подпрограммы инициализации

источника (сторона 1)

Рис.5. Блок-схема алгоритма подпрограммы инициализации

приемника (сторона 2)

(Z)=0, если не готов

(Z)=0, если не готов

(Z)=1, если готов

Рис.6. Блок-схема алгоритма подпрограммы проверки готовности приемника

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.