9Мы преднамеренно оставляем значение "компонента" неуказанным. Это будет зависеть от заключительного проекта ткани: компонент может быть одним или более простыми логическими ворота, или LUTосуществление произвольной логической функции; интерконнекты на ткани также будут "компонентами" в смысле, что они могут также быть дефектными.

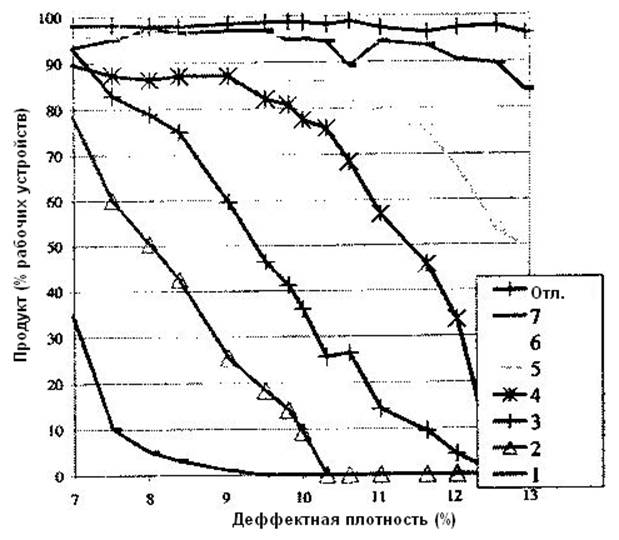

Рис. 19. Данные, достигнутые, изменением удельного веса дефекта и числа дефектов, которые могли рассчитать наши испытательные схемы. Ось X представляет плотность дефекта ткани, ось Y показывает достигнутый данные (или, другими словами, фракция компонентов ткани без дефекта, которая также идентифицирована), и каждая линия представляет счетчик, который может посчитать дефекты до различного порога.

Чтобы проверить эффективность этой процедуры и измерить воздействие порога считающего дефект по результатам, мы запускали много моделирований, результаты которых представлены на рис. 19. Из этих результатов очевидно, что возможно достигнуть высоких выработок даже с испытательными схемами, которые могут посчитать небольшое количество дефектов, особенно если плотность дефекта низка. Например, для удельных весов меньше чем 10%, испытательная схема, которая может считать до четырех ошибок, достигает выхода более чем 80%. Достижимы выходы более чем 95 % при использовании более сильных испытательных схемам.

Эта стратегия тестирования в настоящее время требует времени, пропорционально проверке ткани компонентов, если используется испытательная схема размера. Чтобы ускорить тестирование еще больше, может быть усилено пересоздание ткани. Как только часть ткани нанесена на карту, она может использоваться, чтобы проверить другие части ткани. Это может уменьшить время проверки, устраняя узкое место полосы пропускания вне чипа и учитывая параллельное тестирование.

E. Случай для КМОП /наноперемешанная архитектура.

Новые решения наноэлектроники представляют потенциал для беспрецедентных уровней плотности устройства, низкой мощности вычисления, и возможно высоко-операционной скорости. Несмотря на этот высокий потенциал, для любой новой технологии будет очень трудно конкурировать на равных с крупномасштабной инфраструктурой изготовления кремния, доказанными методологиями проекта, и экономической предсказуемостью.

Альтернативный подход к резкому изменению технологии – интеграция кремния с наноэлектроникой, то есть, смешанные интегральные схемы КМОП /нано. Этот маршрут имел бы гладкий переход и позволил бы усиливать выгодные аспекты обеих технологий [64]. Такой подход воплощен в архитектуре, предложенной Голдштейном [25] и ДеХоном [26]. Мы обращаемся к этой парадигме проекта как nano на КМОП (НнК); подобные идеи также предлагались в [65].

Парадигма НнК учитывает существенную многосторонность проекта. Одно экстремальное использование КМОП – прямое вычисление среды, в то время как нано на вершине используется как приложение для улучшения достижения целей интеграции. Например, нано решетка может действовать как память или как большой логический массив. В другой противоположности наночасть была бы первичной средой вычисления, в то время как лежащая в основе КМОП будет использоваться просто, чтобы обеспечить усиление сигнала и запирающие способности. Этот последний подход – описан в секции V-C. Более уравновешенное решение использует обе среды для первичного вычисления с частями схем, распределенными как в КМОП так и в нано в для более лучшего усиления.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.