Министерство образования и науки Российской Федерации

Балтийский государственный технический университет «Военмех»

им. Д.Ф. Устинова

ИССЛЕДОВАНИЕ ПРОГРАММИРУЕМОГО ТАЙМЕРА

Методическое пособие к лабораторной работе по курсу

«Вычислительные устройства и системы»

Санкт-Петербург

2013

Целью работы является изучение устройства и основных принципов работы программируемого таймера КР580ВИ53, овладение практическими навыками его программирования для задания временных интервалов и формирования сигналов с различными временными параметрами.

Управление периферийными устройствами часто требует от микропроцессорной системы точного задания временных интервалов между управляющими сигналами. Сделать это программно зачастую невозможно из-за сложного временного расписания обмена данными внутри системы. К тому же вставка тактов ожидания в программу тормозит работу процессора. Такие задачи поручают программируемым таймерам (ПТ). С их помощью микропроцессор (МП) может формировать временные интервалы произвольной длительности, производить синхронизацию внешних устройств, организовывать счетчики событий, вести счет текущего времени и т. д.

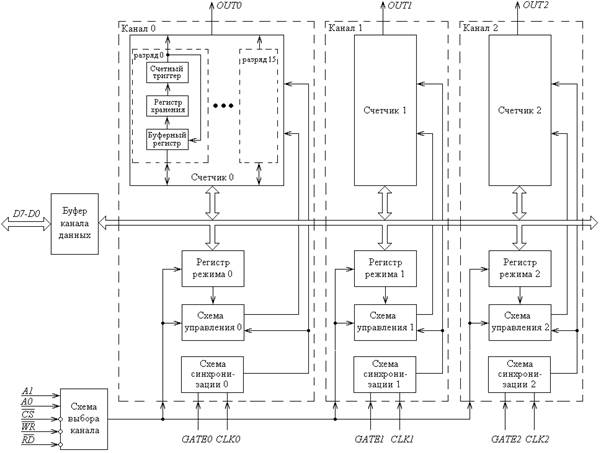

Для задания временных интервалов и формирования сигналов с различными временными параметрами в IBM PC/XT применяется ПТ фирмы Intel − i8253 (отечественный аналог КР580ВИ53), в AT − i8254. С точки зрения программиста они идентичны. Рассмотрим назначение основных узлов ПТ КР580ВИ53 (рис. 1).

Рис. 1. Структурная схема ПТ КР580ВИ53

Схема выбора канала формирует сигналы управления каналами 0, 1 и 2, внутренними и внешними передачами данных, приемом управляющих слов (УС).

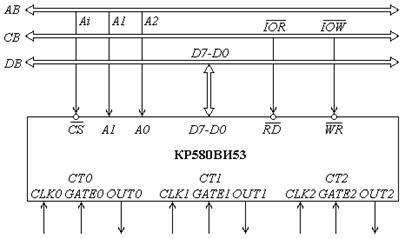

Буфер канала данных состоит из восьми двунаправленных формирователей, имеющих на выходе состояние «Выключено», и осуществляет сопряжение таймера с системной шиной данных МП (рис. 2). Через него осуществляется запись УС в регистры режима и параметров счета в счетчики каждого канала.

Схемы всех каналов идентичны и содержат регистры режима, схемы управления, схемы синхронизации и счетчики.

Рис. 2. Подключение ПТ к шинам МП

Регистр режима канала состоит из шести разрядов (D5−D0) и предназначен для приема и хранения УС, код которого задает режим работы канала, определяет тип счета и последовательность загрузки данных в счетчик. Информацию в регистр режима можно только записывать. Прочитать содержимое этого регистра невозможно.

Схема управления канала синхронизирует работу счетчика в соответствии с запрограммированным режимом и работу канала с работой МП.

Схема синхронизации канала формирует серию внутренних тактовых импульсов определенной длительности, которая зависит от внешней частоты синхронизации CLK и определяется внутренними времязадающими цепями схемы. Максимальная частота внешних сигналов синхронизации CLK не более 2 МГц.

Счетчик канала представляет собой 16-разрядный вычитающий счетчик с предустановкой, предназначенный для выполнения счетных операций в соответствии с запрограммированным режимом работы в двоичном или двоично-десятичном коде над однобайтным или двухбайтным числом. Возможная скорость счета – от 0 до 2 МГц. Максимальная величина счета при работе в двоичном коде составляет 216=65536, в двоично-десятичном коде – 10000. Счетчики каналов независимы друг от друга и могут иметь различные режимы работы и типы счета. Запуск счета в каждом канале, его останов и продолжение осуществляется по соответствующему сигналу GATE ("Разрешение канала").

Разряд счетчика состоит из трех каскадов (рис. 1): буферного регистра, регистра хранения и счетного триггера.

Счетный триггер принимает информацию из регистра хранения. Так как счетчик вычитающий, то число, загруженное в счетный триггер, будет декрементироваться. Загрузка во все ряды счетных триггеров информации в виде нулей позволяет получить максимально возможную величину счета. Информация из счетного триггера передается в буферный регистр и при необходимости может быть прочитана.

В регистр хранения информация поступает из буферного регистра (обратная операция невозможна). Содержимое регистра хранения изменяется только при перезагрузке счетчика новой величиной или при перепрограммировании режима работы канала (запись УС в регистр режима). В последнем случае регистр хранения устанавливается в нулевое состояние.

Буферный регистр принимает данные, поступающие из МП, и передает их в регистр хранения или, наоборот, принимает информацию из счетного триггера и передает ее в МП.

Назначение выводов ПТ (рис. 2):

D7−D0 (шина данных) – двунаправленная трехстабильная, подключаемая к системной шине данных и предназначенная для приема УС и данных из МП и передачи данных в виде показаний счетчиков из микросхемы в МП, D0 – младший разряд.

A0, A1 (входы адреса)

Входные сигналы, поданные на эти выводы, определяют адресацию внутри микросхемы при задании режима работы каждого из каналов таймера (табл. 1). Обычно их соединяют с двумя младшими разрядами системной адресной шины.

![]() ("Выбор устройства")

("Выбор устройства")

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.