Министерство образования и науки Российской Федерации Федеральное агентство по образованию Государственное образовательное учреждение высшего профессионального образования «Новосибирский государственный технический университет»

Кафедра радиоприемных и радиопередающих устройств

Лабораторная работа №2 «Арифметические сумматоры»

по дисциплине «Цифровые устройства и микропроцессоры»

Факультет: РЭФ Группа: РТ5-01

Студент: Воробьёва Ю.С.

Преподаватель: Снурницин В.Р.

Новосибирск, 2013

Цели работы: Изучение принципов построения схем мультиплексоров и демультиплексоров и ознакомление с их применениеми. Исследование схем мультиплексоров и демультиплексоров в виртуальной электоронной лаборатории EWB.

Ход работы.

1. Начертить логическую схему MUX 2-1, подключить её входы к генератору кодовых слов и к логическому анализатору, к которому подключается ещё выход. Протестировать работу мультиплексора. Сохранить как макромодель MUX 21. То же самое проделать для DMUX 1-2, сохранив её как макромодель DMUX12.

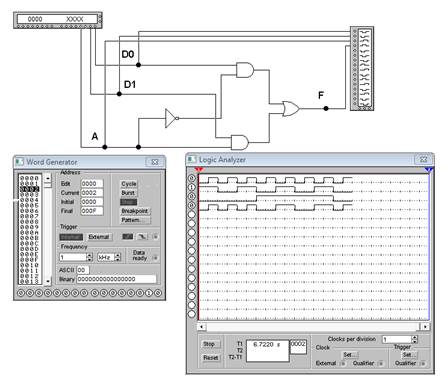

Рис.1. Логическая схема мультиплексора 2-1. MUX 2-1.

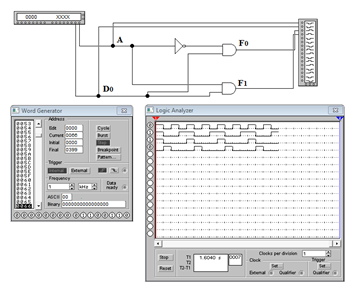

Рис.2. Логическая схема демультиплексора 1-2. DMUX 1-2.

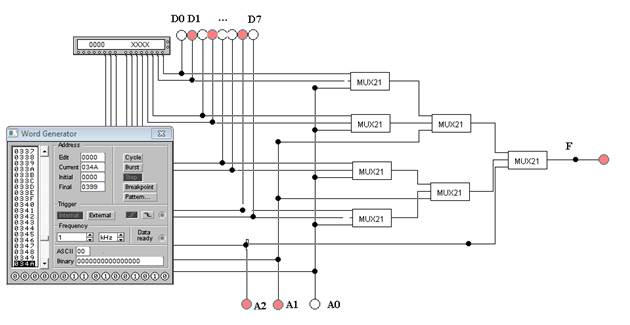

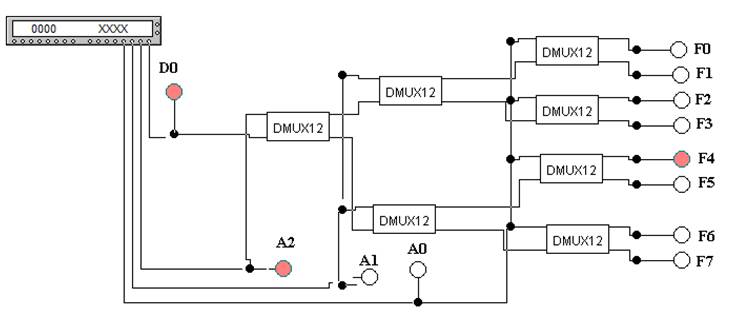

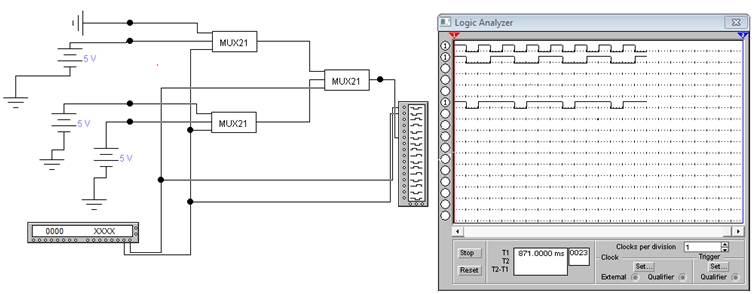

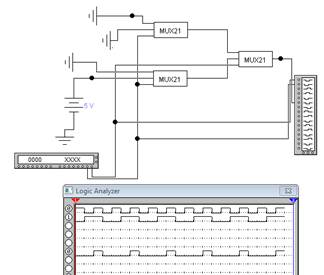

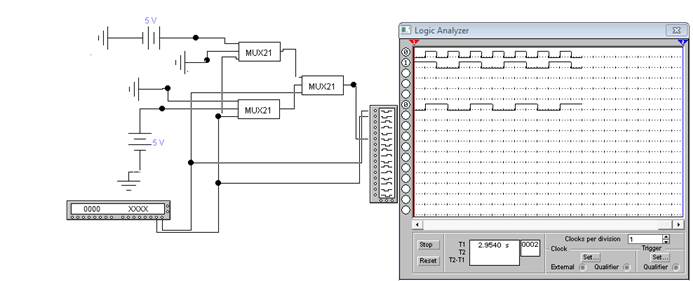

2. Самостоятельно составить логическую схему MUX 8-1 из MUX 2-1, начертить её и протестировать. Сохранить как макромодель MUX81. То же самое проделать для логической схемы DMUX 1-8, составив её из DMUX 1-2 и сохранив её как макромодель DMUX18.

Рис.3. Логическая схема MUX 8-1.

Рис.3. Логическая схема DMUX 1-8.

3. Самостоятельно реализовать на MUX 2-1 функции логического сложения, умножения и мажоритарную функцию от трёх переменных. Протестировать схемы с помощью логического преобразователя.

Рис.4. Функция логического сложения, реализованная на MUX 2-1.

Рис.5. Функция логического умножения, реализованная на MUX 2-1.

Рис.6. Функция равнозначности, реализованная на MUX 2-1.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.