Вопрос номер 15 к государственному экзамену по ТП ЭВМ.

15. Логическая, функциональная и физическая реализация 16-ти разрядных интерфейсов Intel.

Интерфейсные системы Multibus фирмы Intel с архитектурой Multibus I

и Multibus II предназначены для построения магистрально-модульных многопроцессорных систем, в основном использующих микропроцессоры (МП) типов 8080, 8085, 8086, 80286, 80386.

1) Архитектура Multibus I содержит 5 магистралей: 2 параллельные

Multibus и LBX, многоканального ввода-вывода (BB) Multichannel, локального (BB) SBX и последовательную Bitbus.

2) Multibus II разработан для высокопроизводительных мультипроцессорных систем. Архитектура Multibus II содержит 6 независимых магистралей: 2 параллельные, PSB и LBXII, последовательную системную SSB и 3 магистрали, заимствованные из архитектуры Multibus I : многоканального ВВ Multichannel, локального ВВ SBX, и последовательного Bitbus. Структура каждой магистрали не зависит от типа МП и учитывает требования будущих МП. Одновременное использование магистралей обеспечивает пропускную способность 96 Мбайт/с (PSB - 40 Мбайт/с, LBXII- 48 Мбайт/с, Multichannel - 8 Мбайт/с).

Благодаря большей пропускной способности в системе можно использовать много процессорных модулей без перезагрузки магистрали. Поскольку применяемые процессорные модули приобретают все более широкие функциональные возможности, запас по пропускной способности позволяет наиболее эффективно использовать каждый добавляемый модуль для повышения производительности системы.

Главное по вопросу:

а) Системная магистраль Multibus - одна из наиболее распостраненных интерфейсов в мире.Интерфейс обеспечивает программный обмен данными одного или нескольких процессоров с памятью и с контроллерами ввода/вывода, прямой доступ к памяти (ПДП) и генерацию прерываний. Он использует два независимых адресных пространства (памяти и ввода/вывода) и обеспечивает прямую адресацию до 16 Мбайт памяти с использованием 16-ти разрядного адреса. В циклах

ПДП и В/В возможны 8- и 16- разрядные передачи данных. Интерфейс основывается на принципе "задатчик-исполнитель", использует асинхронный протокол, мультипроцессорные возможности, раздельные шины адреса и данных.

Интерфейс выполняет следующие функции:

арбитраж запросов задатчиков на управление интерфейсом, операции смены задатчика, обмен данными(чтение и запись),байтовые передачи данных в двухбайтовых системах, операции с запретом обращения, операции прерывания. Существует 4 типа операций данных:

1) Чтение из ЗУ

2) Чтение из портов В/В

3) Запись в ЗУ

4) Запись в порты В/В

Реализованы две схемы системы прерываний:

-невекторное(используется одна линия запроса прерываний) -векторное(используется передача вектора прерывания по линиям данных)

Также существуют две схемы арбитража: последовательный(определяется электрической близостью к арбитру) и параллельный (определяется приоритетом запроса).В интерфейсе осуществлен циклический приоритет и возможны два режима работы:

-монопольный-задатчик, захвативший интерфейс блокирует все попытки захвата интерфейса другим задатчиком,на всем продолжении своей работы

-мультиплексный-задатчики поочередно владеют магистралью в соответствии с приоритетами.

Скорость передачи до 5 Мслов/с (8- или 16-разрядных) в 24-разрядном адресном пространстве.

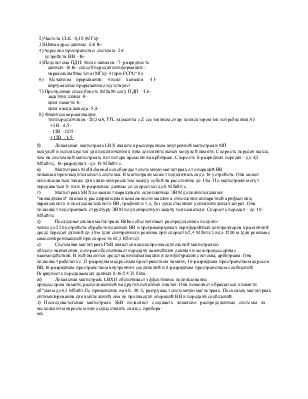

Физическая реализация интерфейса в полной мере отражена( при использовании Multibus I) на ISA шине:

1)Протокол обмена данными -синхронный2)Частота CLK -8,10 (МГц)3)Шина адрес/данные -24/164)Адресное пространство: системы -24устройств В/В -165)Подсистема ПДП: число каналов -7- разрядность данных -8/16- способ передачи информации -паралельныйчастота (МГц) -4(при FCPU=8)6) Механизм прерывания: число каналов -11- виртуальные прерывания отсутствуют

7) Пропускная способность (Мбайт/сек): ПДП -1,6задатчик шины -8цикл памяти -8цикл ввода/вывода -5,48) Физическая реализация:

тип передатчиков -20;5мА,TTL элементы с Z состоянием,откр. коллекторомток потребления(А):

+5В -4,5-12В -0,05+12В -1,5-

б) Локальная магистраль LBX является расширением внутренней магистрали МП

модулей и используется для подключения к ним дополнительных модулей памяти. Скорость передач выше, чем на системной магистрали, нет потерь времени на арбитраж. Скорость 8-разрядных передач - до 9,5 Мбайт/с, 16-разрядных - до 19 Мбайт/с.

в) Магистраль Multichannel освобождает системную магистраль

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.