В алгоритме присутствуют операции сложения и вычитания, в связи с этим необходимо использовать сумматоры на основе ИМС 1533ИМ3 с СУП. Так как разрядность шины 32 бита, а стандартные сумматоры 4 битные, то придется увеличивать разрядность сумматора путем параллельного включения данных ИМС.

Состояния сумматора ИМ3

|

Вход |

Выход |

||||

|

Сn |

Bn |

An |

!Cn+1 |

!Sn |

Sn |

|

0 |

0 |

0 |

1 |

1 |

0 |

|

0 |

0 |

1 |

1 |

0 |

1 |

|

0 |

1 |

0 |

1 |

0 |

1 |

|

0 |

1 |

1 |

0 |

1 |

0 |

|

1 |

0 |

0 |

1 |

0 |

1 |

|

1 |

0 |

1 |

0 |

1 |

0 |

|

1 |

1 |

0 |

0 |

1 |

0 |

|

1 |

1 |

1 |

0 |

0 |

1 |

Для того чтобы организовывать сложения, либо вычитание применяют специальные схемы «сумматор – регистр», т.е. так называемый накапливающий сумматор. Вычитание будет производится путем добавления в схему накапливающего сумматора элемента «исключающие или»(к155лп5).

Отдельно отмечу, что выбор знака у результата будет осуществлен с помощью 3х составных регистров и дешифратора, где выборка будет осуществляться по значению счетчика CTL.

Размер ПЗУ для хранения констант алгоритма должно быть размером 32х32 (расширенное пзу к155ре3).

Для выборки констант потребуется 4 – х разрядный счетчик (к155ие7).

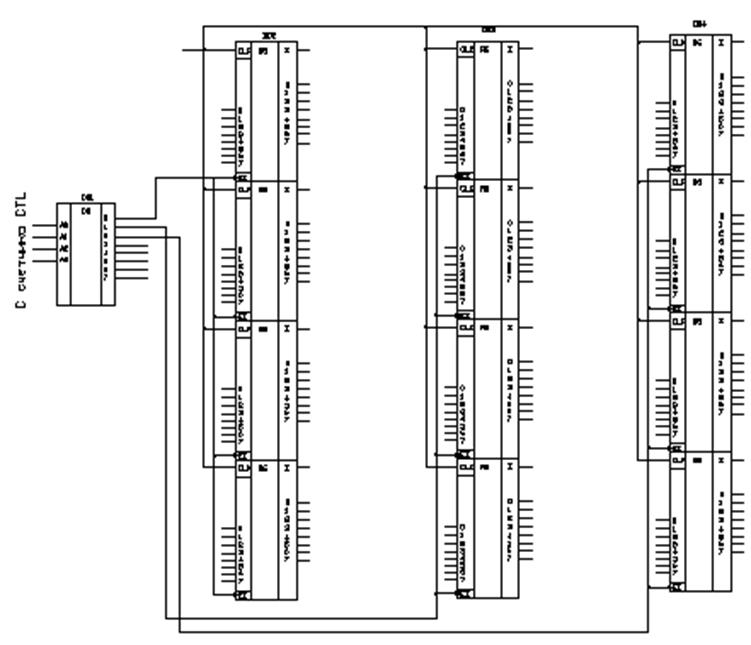

Проектирование принципиальной схемы устройства

Для начала проектирования необходимо составить регистровую схему по алгоритму описанному выше.

Рисунок 3

Описание числа

Как я уже отмечал, число необходимо выбрать 32 битное. Итак, у нас используются два вида чисел во всем алгоритме - это числа, которые представлены главным образом целой частью (входящий угол: 90) и числа, у которых в основном информационная часть после запятой (0,1111).

В общем вид числа следующий:

Рисунок 4

Точность 22 бит как раз хватает чтобы описать константы.

9 бит – это число 512 (для входящего угла вполне достаточно), что удовлетворяет техническому заданию, то есть ограничение на существование аргумента: от 360 до -360.

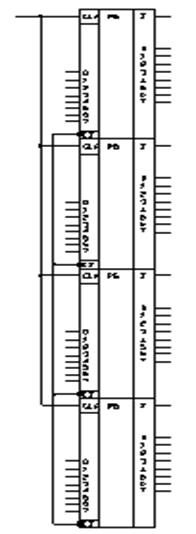

Реализация 32 битных регистров

Для образования 32

битных регистров достаточно их соединить параллельно, причем у них общие

управляющие сигналы CLK, EZ.

Для образования 32

битных регистров достаточно их соединить параллельно, причем у них общие

управляющие сигналы CLK, EZ.

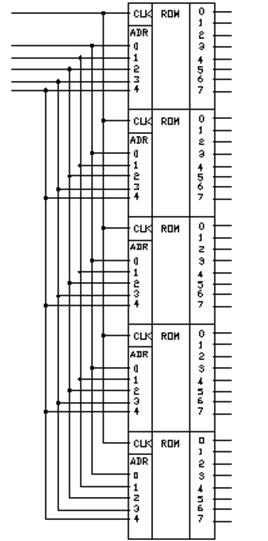

Реализация 32 битного модуля памяти

Для реализации 32

разрядного ПЗУ необходимо соединить их адресные входы. Таким образом

получается, что по тому и тому же адресу в 5 – ти ПЗУ хранятся 5 частей нашего

числа. В данному случае рассмотрена реализация 32 битного ПЗУ из 32х8 (К155РЕ3)

Для реализации 32

разрядного ПЗУ необходимо соединить их адресные входы. Таким образом

получается, что по тому и тому же адресу в 5 – ти ПЗУ хранятся 5 частей нашего

числа. В данному случае рассмотрена реализация 32 битного ПЗУ из 32х8 (К155РЕ3)

Выборка выхода:

Выборка осуществляется в соответствие со значением на счетчике CTL, поэтому перед выходом идет команда считать со счетчика значение, послать на дешифратор, а дальше дешифратор выбирает какой из регистров падать на выходной 16 битный регистр.

Проектирование управляющего ПЗУ

У нас имеется 21 блок, которые в той или иной последовательности взаимодействуют. Каждому блоку присвоен свой уникальный номер в двоичной системе счисления. Таким образом, в управляющем ПЗУ – адресами будут такт операции, а выходящие сигналы – сигналы управления, включающие определенные элементы в соответствие с алгоритмом.

Нам необходимо ПЗУ для хранения команд размером 32х32. (расширенная к155ре3)

Для начала нам необходимо определиться с частотой управлявшего ПЗУ, так как это очень важный параметр в том плане, что несоответствие по быстродействию у большинства выбранных элементов относительно большое. Поэтому нам необходимо выбрать оптимальную частоту работы этого ПЗУ. Самым медленным в схеме будет сумматор, а значит, он и будет определять частоту работы. Поэтому частота будет равна 18 МГц.

Составим следующую таблицу:

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.