В современных условиях постоянно увеличивающихся потребностей в высокоскоростных вычислениях обычные процессоры с небольшой разрядной сеткой (8 разрядов) могут не удовлетворять требованиям по скорости выполнения математических операций с плавающей запятой. Использование же готовых интегральных математических (со)процессоров в ряде случаев может оказаться затруднительным в связи с необходимостью присутствия дополнительной полноценной «обвязки» (память, центральный процессор для осуществления операций ввода-вывода и др.). Конструирование же специального математического процессора для выполнения какой-либо одной функции в интегральном исполнении весьма дорогостояще и для единичных экземпляров либо малосерийного производства оказывается нерентабельно. В таком случае решением проблемы может стать процессор, собранный на элементах репрезентативных серий. Пример такого процессора с заданными характеристиками для вычисления функции X+Y и приводится в данной работе.

Процессор может быть применен, например, в системе сбора и обработки данных для их предварительной обработки в качестве накопителя (аккумулятора).

1. Техническое задание

Необходимо разработать специализированный процессор для выполнения операции алгебраического сложения чисел с плавающей запятой.

- система счисления – двоичная;

- разрядная сетка процессора – 8 разрядов;

- порядок числа – 8 разрядов, мантиссы – 24 разряда;

- код – дополнительный;

- смещенный порядок числа.

Ввод-вывод данных осуществляется через совмещенную двунаправленную шину данных.

При проектировании в базовой части схемы применять следующие типы логики:

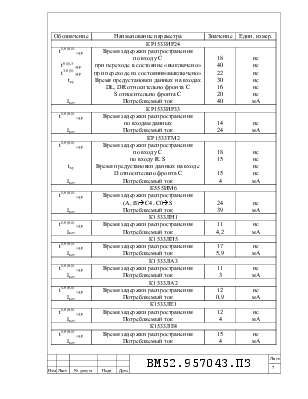

- микромощная ТТЛШ серии 1533 в пластиковом корпусе;

- в обоснованных случаях – любые другие типы логики.

Проектируемый процессор оптимизировать по быстродействию, используя средства:

- улучшение структуры устройства;

- применение в узких местах микросхем повышенного быстродействия.

Предусмотреть установку схемы в исходное состояние при включении и сбое по питанию.

Предусмотреть фильтр цепей питания.

В разработке применить кварцевый генератор.

Выработать рекомендации по следующим свойствам процессора:

- размеры и характер размещения проводников, размещение фильтрующих конденсаторов в пределах платы;

- расположение микросхем по отношению к охлаждающему потоку воздуха;

- рекомендации по обеспечению тепловых режимов.

2. Анализ вариантов реализации процессора

Процессор состоит из следующих основных блоков:

- блок буферов ввода – вывода;

- блок обработки порядков;

- блок регистров мантисс;

- блок сложения;

- блок управления.

Буферы ввода – вывода служат для согласования сигналов на локальных шинах процессора с внешней шиной данных, буферизации сигналов, а также организация двунаправленного обмена через шину данных с разделением входного и выходного потока на различные локальные шины. Блок представляет собой два однонаправленных буфера с возможностью переключения выхода в состояние высокого сопротивления.

Блок обработки порядков содержит: регистр и двунаправленные счетчики с параллельной загрузкой для организации хранения и инкремента/декремента порядков при выравнивании мантисс перед сложением. Наиболее простым является вариант реализации, когда оба порядка слагаемых хранятся непосредственно в счетчиках, производится сравнение порядков на цифровом компараторе и инкремент меньшего из порядков с одновременным сдвигом соответствующей мантиссы. Однако этот вариант предусматривает сравнение чисел на каждом из шагов, пока они не станут равны. Анализ функционирования такой схемы показал, что компаратор – устройство достаточно медленное, и работа такой схемы оказывается также весьма медленной. Так как данная операция производится в цикле до полного выравнивания порядков, схема не может быть принята из соображений быстродействия. Поэтому была применена схема, в которой загрузка одного из порядков производится в регистр. После получения порядка второго числа происходит их вычитание, и результат записывается в счетчик. Затем, если разность не равна нулю, производится счет в нужном направлении до получения нулевого результата. При этом вычитание порядков производится только однократно, а проверка на нуль осуществляется весьма быстро комбинационной логикой, что позволяет сократить длительность такта.

Блок регистров мантисс состоит из двух 24 – разрядных универсальных регистров, служащих для хранения и сдвига мантисс перед сложением. Кроме того, на одном из регистров производится хранение результата после сложения и его нормализация. Возможно применение различных регистров для хранения мантисс до- и после сложения, однако это увеличивает аппаратные затраты при незначительном увеличении быстродействия за счет отказа от мультиплексора выбора источника данных для записи в регистр. Вместо регистров сдвига для осуществления этой операции возможно применение 24-х канального 24-х разрядного мультиплексора, на входах которого формируются уже сдвинутые (монтажным сдвигом) значения мантисс, а адресными входами осуществляется выбор нужного значения; но аппаратные затраты данной схемы неоправданно большие, и применение такая схема может найти только в составе БИС высокоскоростного специализированного процессора.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.