RAS# (ROW Address Strobe) – сигнал, низким уровнем которого определяется наличие действительного (VALID) адреса строки на мультиплексированной шине MA.

CAS# (COLUMN Address Strobe) – низкий уровень характеризует наличие адреса столбца на шине адреса MA.

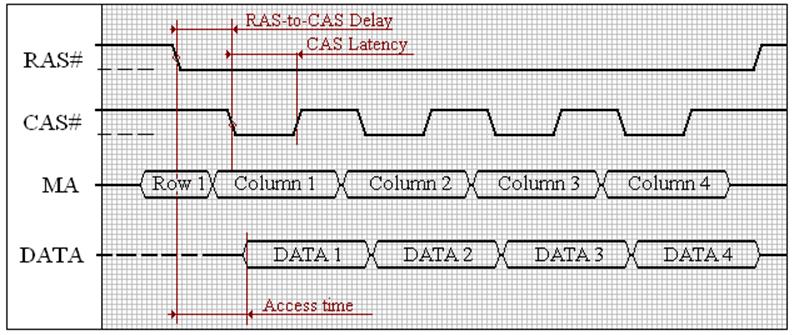

Циклы работы стандартной DRAM (Dynamic Random Access Memory):

Удержание в активном состоянии сигнала RAS# говорит о том, что для каждого изменяющегося адреса столбца сохраняется текущем адрес строки.

Существуют несколько параметров, характеризующие быстродействие динамической памяти:

§ RAS-to-CAS Delay – временная задержка появления CAS# относительно появления активного сигнала RAS#.

§ CAS Latency – время, определяющее удержание сигнала CAS# в активном состоянии.

§ Access Time – время реакции памяти, определяется вышеперечисленными параметрами и некоторыми другими, которые настраиваются в BIOS Setup.

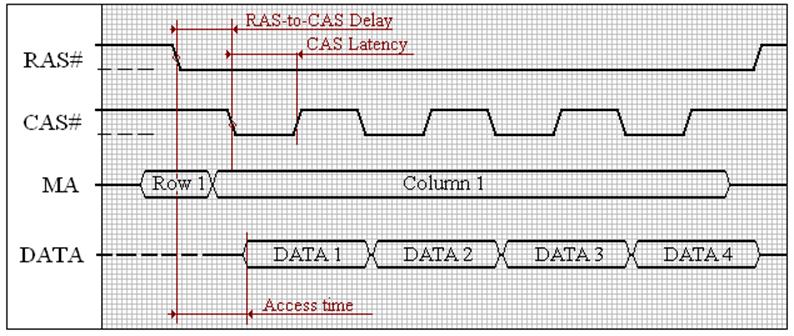

Существует расширенная модификация динамической памяти, циклы которой отличаются от циклов стандартной DRAM:

Основное отличие заключается в том, что выставляется адрес только первого блока данных с автоинкрементом адреса внутри микросхемы памяти. На автоинкремент влияет изменяющийся во времени сигнал CAS#, сообщая о последовательной выборки данных из одной строки при последовательном переборе столбцов.

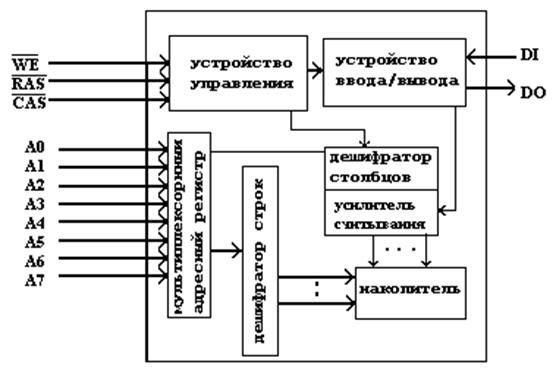

Внутренняя организация микросхемы памяти:

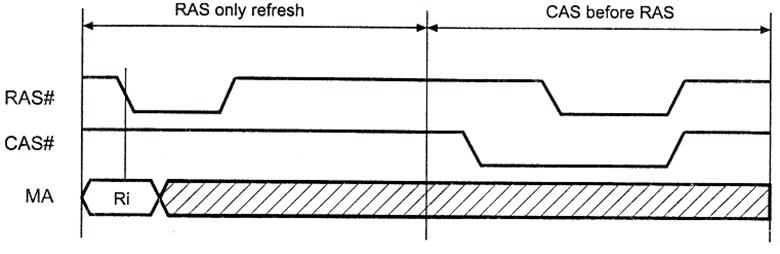

4. Регенерация динамической ОЗУ:

Время, в течении которого самопроизвольно разряжается паразитная емкость, составляет порядка 2 мс, поэтому через каждые 2 мс необходимо регенерировать информацию. С этой целью введены специальные циклы обращения к памяти – циклы регенерации (Refresh Cycles):

Циклы регенерации характеризуются регулярными (с определённой периодичностью запускающимися независимо ни от чего) холостыми циклами обращения к памяти.

Существует несколько разновидностей циклов регенерации:

§ Цикл RAS Only Refresh - является классическим, без импульса CAS# (на рис. слева). В этом случае адрес регенерируемой колонки выставляется контроллером памяти до спада сигнала RAS# очередного цикла регенерации.

§ Цикл CAS Before RAS – поддерживаемый практически всеми современными микросхемами памяти (на рис. справа). В этом случае установление активного состояния сигнала RAS# происходит уже во время действия сигнала CAS# (В обычном цикле обращения такой ситуации не возникает). В этом случае микросхема выполняет адрес строки, который находится во внутреннем счётчике микросхемы, и в задачу контроллера входит только периодическое формирование таких циклов. Во время спада сигнала RAS# сигнал WR# должен находится в неактивном состоянии. Дополнительным преимуществом данного цикла является экономия потребляемой мощности за счет неактивности внутренних адресных буферов.

5. Программируемые Логические Матрицы (ПЛМ)

ПЛМ – программируемые логические матрицы. Ранее их относили к классу ПЗУ. В них используются не перемычки, а набор логики И-НЕ, ИЛИ-НЕ. Используя их, можно запрограммировать любую функцию. ПЛМ используются для создания микроавтоматов.

На сегодня существуют ПЛМ не только с логическими входами, но и с ячейками памяти. Их недостаток – по выключение питания данные теряются, поэтому должно быть ПЗУ для начальной загрузки. Таким образом, можно реализовать МП с любой системой команд, которую можно менять в процессе работы.

6. Многопортовая ОЗУ.

Многопортовая ОЗУ применяется в серверах и изредка в современных компьютерах. Суть технологии – наличие нескольких независимых каналов связи ОЗУ и устройств. Используется для распараллеливания обмена данными с ОЗУ. Например, ОЗУ делится на 2 части, работающие независимо. При обращении 2-х устройств к одной области начинает работать приоритетная система либо по времени, либо по приоритету.

Список дополнительной литературы:

1.Гук М. Аппаратные средства IBM PC. Энциклопедия,2-е изд.-СПб.: Питер, 2001.-928с.: ил.

2.Шевкопляс Б.В. Микропроцессорные структуры. Инженерные решения: Справочник. - 2-е изд. перераб. и доп. – М.: Радио и связь, 1990.-512 с.: ил.

3.Морисита И. Аппаратные средства микроЭВМ: Пер. с япон.-М.: Мир, 1988.-280 с., ил.

4.Организация ЭВМ. 5-е изд./К.Хамахер, З.Вранешич, С.Заки.-СПб.: Питер; Киев: Издательская группа BHV, 2003.-848 c.: ил. – (Серия “Классика computer science”).

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.