§ Цикл чтения из стека – цикл чтения с ЗУ по содержимому указателя стека (активные флаги: MEMR, STACK);

§ Цикл записи в стек (активные флаги: WO#, STACK);

§ Цикл ввода IN – ввод данных с устройства (запись в аккумулятор) в МП (активные флаги: IN);

§ Цикл вывода OUT – выдача данных с МП (запись) во внешнее устройство(активные флаги: OUT, WO#);

§ Цикл прерывания INT – прием кода команды RST или CALL из контроллера прерываний (активные флаги: M1, INTA);

§ Цикл остановa HLT (активные флаги: MEMR, HLTA);

§ Цикл прерывания при останове (активные флаги: INTA, HLTA, M1).

5. Организация работы МП в различных циклах.

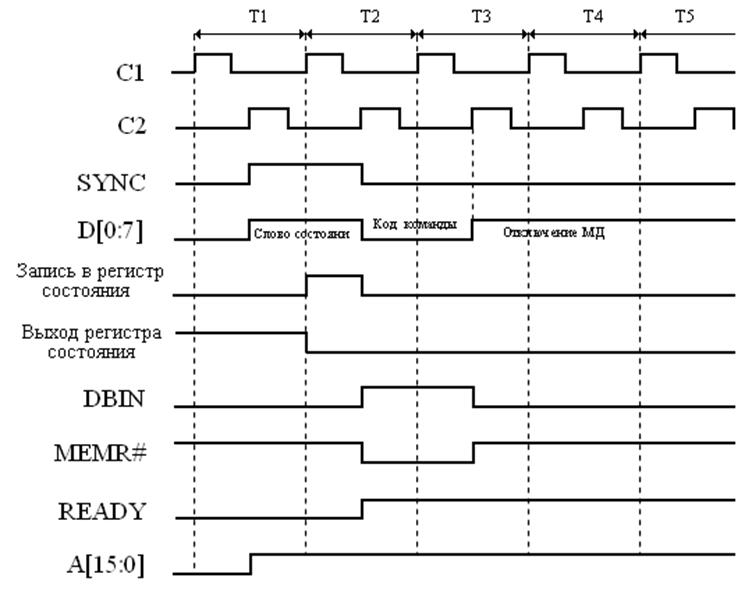

5.1. Извлечение кода команды из памяти или внешнего устройства:

§ На такте T1 программный счетчик выдает на МА адрес ячейки памяти, из которой будет считываться код команды. При этом схема приращения адреса МП автоматически увеличивает на единицу значения числа, записанного в программном счетчике. Положительным фронтом сигнала C2 формируется сигнал SYN и выдается слово состояния на МД. Сигнал DBIN, управляющий двунаправленным шинным формирователем дешифратора магистрали данных, на такте равен нулю, что позволяет слову состояния поступать на МД.

§ На такте T2 слово состояния записывается в регистр. Положительным фронтом сигнала C2 прекращается сигнал SYNC и формируется единичный сигнал DBIN, позволяющий данным поступить на вход мп через дешифратор. Из сигнала «прием» и седьмого бита слова состояния D7 формируется сигнал на чтение данных из памяти (MEMR), позволяющий данным поступать из памяти на МД. Изменения данных на этом такте восприниматься МП не будут, так как их запись осуществляется в фиксированные моменты времени на такт T3. На этом же такте анализируется состояние сигналов «готов», «захват» и «общий останов». При нулевом сигнале в четвертом бите слова состояния D4 и единичном сигнале на входе «готов» мп переходит к выполнению такта T3. Если к моменту появления отрицательного фронта сигнала C2 на такте T2 сигнал на входе «готов» будет иметь значение «0», то МП на такте T2 переходит в режим ожидания. В этом режиме приостанавливается процесс обработки данных и формируется единичный сигнал на выходе «ожидание», подтверждающий это состояние. Время ожидания выражается целым числом тактов и может длиться бесконечно долго. На каждом такте в этом режиме при отрицательном фронте C2 будет проверяться состояние сигнала на выходе «готов».

§ На такте T3 в момент отрицательного фронта сигнала C1 производится запись данных во внутренний регистр кода команды. Положительным фронтом сигнала C2 прекращается сигнал «прием» на выходе мп и, следовательно, сигнал DBIN. Импульсы на выходе DBIN будут формироваться мп в машинных циклах: извлечения кода команды, чтения данных из памяти, прерывания, чтения из стека или внешнего устройства.

§ На последующих тактах дешифратор кода команды расшифровывает код команды, определяет число байт в команде, формирует команды и внутренние пересылки данных и подготавливает мп к выполнению следующих машинных циклов.

§ Отличие машинных циклов чтения данных из памяти, стека или внешнего устройства от цикла M1 будет в том, что мп будет воспринимать числа, полученные на такте T3 по МД, не как код команды, а как данные. При чтении данных из внешнего устройства формируется сигнал чтения УВВ из сигнала DBIN и в 6 байта слова состояния. Этот сигнал позволяет внешнему устройству выдать информацию на МД.

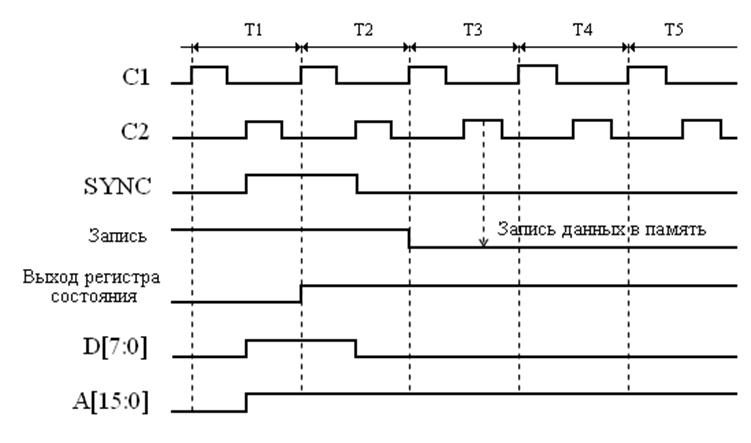

5.2. Запись данных в память или ВУ.

§ На такте T1 содержимое регистра адреса МП выдается на МА, а на МД выдается слово состояния.

§ На такте T2 на МД выдаются данные для записи в память.

§ На такте T3 формируется сигнал, по которому происходит запись данных в память или ВУ.

На протяжении всего машинного цикла записи данных в память сигнал «прием» имеет значение «0», что позволяет шинному формирователю работать в режиме выдачи данных на МД. Процесс записи данных на ВУ аналогичен записи данных в память с той лишь разницей, что для формирования сигнала записи в УВВ сигнал с выхода WR и четвертый бит D4 слова состояния.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.