3.1 Тактирование схемы/исполнение команд по тактам

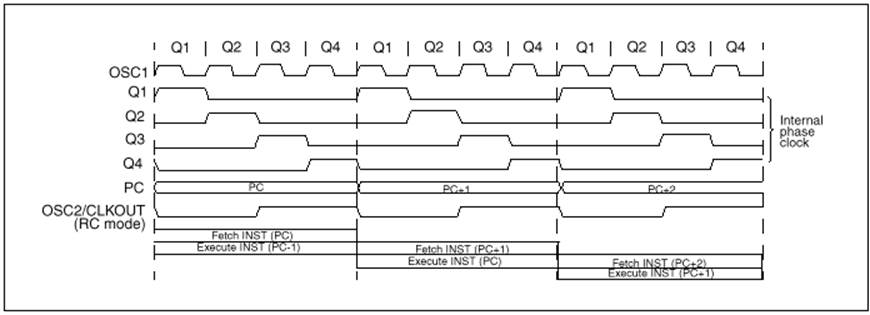

Машинный такт ( из OSC1) внутри делится на четыре, чтобы сгенерировать четыре не-перекрывающихся такта, названных Q1, Q2, Q3 и Q4. Программный счетчик (PC) увеличивается каждый Q1, инструкция выбирается из программной памяти и записывается в регистр команд в Q4. Инструкция декодируется и выполняется в течение следующего Q1 через Q4. Часы и поток выполнения инструкции показывается в Рисунке 3-2.

Рис.3.2.

3.2 Конвейер команд

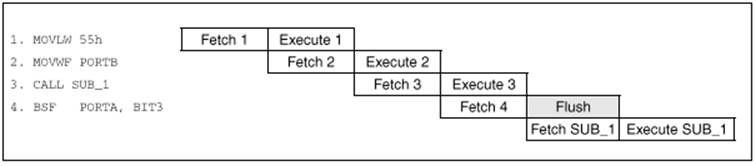

Машинный цикл состоит из четырех циклов (Q1, Q2, Q3 и Q4). Команда выбирается и выполняется на конвейере следующим образом: выбирается за один цикл команда, но пока она декодируется и выполняется, выбирается следующая команда. Тем не менее, из-за конвейера, каждая команда эффективно выполняется в одном цикле. Если команда заставляет перегрузить программный счетчик (например,GOTO), требуется два цикла, чтобы завершить инструкцию (Пример 3-1).

Цикл выборки начинается с Программным Счетчиком (PC), увеличивающимся в Q1.

В цикле выполнения, выбранная команда записывается в Instruction Register в цикле Q1. Эта инструкция затем декодируется и выполняется в течение Q2, Q3, и циклов Q4. Память данных читается в течение Q2 (операнд читается) и записывается в течение Q4 (целевая запись).

Пример 3.1.

4 ОРГАНИЗАЦИЯ ПАМЯТИ

Есть два блока памяти в PIC16F8X. Они – память программ и память данных. Каждый блок имеет собственную шину, так, что доступ к каждому блоку может произойти в течение одного и того же цикла генератора. Память данных может в дальнейшем подразделяться в универсальное РАМ и специальные функциональные регистры (SFRs). Функционирование SFRs, которыми управляет ядро, описано здесь. SFRs, используемые для управления периферийными модулями, описаны в разделе, обсуждающем каждый индивидуальный периферийный модуль.

Область памяти данных также содержит данные EEPROM памяти. Эта память непосредственно не отображается в память данных, но косвенно отображена. Так, косвенный указатель адреса определяет адрес данных EEPROM памяти для чтения/записи. 64 Байта данных EEPROM памяти позволяют адресу колебаться в пределах 0h-3Fh.

4.1 Программная организация памяти

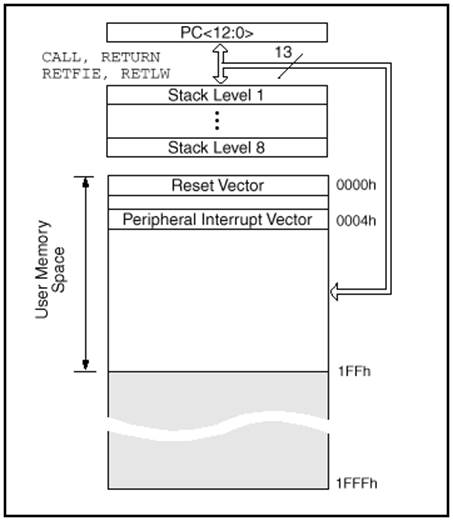

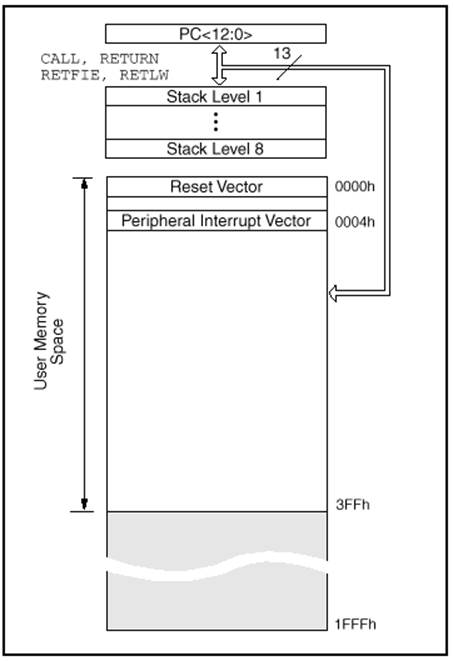

PIC16FXX имеет 13-битовый программный счетчик, способный указать программную память 8Kx14. Для PIC16F83 и PIC16CR83 первые 512 x 14 (0000h-01FFh) реализованы физически (Рисунок 4-1). Для PIC16F84 и PIC16CR84 первые 1K x 14 (0000h-03FFh) – реализованы физически (Рисунок 4-2). Попытка указать позицию выше физически осуществленного адреса вызовет циклический переход.Например, для PIC16F84 обращение на 20h, 420h, 820h, C20h, 1020h, 1420h, 1820h, и 1C20h будет одной и той же инструкцией.

Вектор сброса - в 0000h и вектор прерывания 0004h.

РИСУНОК 4-1: ПРОГРАММНАЯ КАРТА ПАМЯТИ И СТЕК - PIC16F83/CR83

РИСУНОК 4-2: ПРОГРАММНАЯ КАРТА ПАМЯТИ И СТЕК - PIC16F84/CR84

4.2 Организация Памяти Данных

Память данных разделяется в две области. Сначала - специальная область функциональных регистров (SFR), далее - область универсальных регистров (GPR). SFRs управляет функционированием устройства. Части памяти данных группируются. Это доступно как для области SFR, так и области GPR. Область GPR группируется, чтобы достигнуть больше чем 116 байт универсального РАМ. Банковские области SFR - для регистров, которые управляют периферийными функциями. Банковский требует использование управляющих битов для банковского выбора. Эти управляющие биты располагаются в Регистре СТАТУСА. Рисунок 4-1 и Рисунок 4-2 показ организация карты памяти данных. Инструкции MOVWF и MOVF могут переместить величины из регистра W в любой позиции в файле регистра (УFФ), и наоборот. Целая память данных может быть доступной или непосредственно, используя абсолютный адрес каждого файла регистра, или косвенно через Файловый Регистр Выбора (FSR) (Раздел 4.5). Косвенная адресация использует настоящую величину битов RP1:RP0 для доступа в банковские области памяти данных. Память данных разделяется в два банка, которые содержат универсальные регистры и специальные функциональные регистры. Банк 0 выбирается клиринговым битом RP0 (STATUS<5>). Установка бита RP0 выбирает Банк 1.Каждый Банк расширяется вплоть до 7Fh (128 байтов). Первые двенадцать позиций каждого Банка резервируются для Специальных Функциональных Регистров. Остаток – Универсальные регистры, выполненные как статическая RAM.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.