«Микропроцессоры: Операционное устройство (ОУ)»

Варианты реализации МП систем:

1. Однокристальное исполнение.

2. Многокристальные МП

3. Секционные МП

Все типы МП состоят из:

1. Устройство управления (УУ) //отвечает за систему команд

2. Операционное устройство (ОУ) //отвечает за разрядность

3. Интерфейсное устройство для связи МП с внешним миром

1. Сумматоры как основной элемент АЛУ

Выполняет операции над двоичными числами.

1.Сложение

A+B=C

2.Вычитание

A–B=A+(![]() +1)

+1)

3.Сравнение

A–B=? (Чтобы узнать кто больше делаем разность и смотрим знак, через регистр признаков).

Операциями над числами в микропроцессорах занимается специальное устройство - АЛУ (Арифметико-Логическое Устройство), которое базируется на многоразрядном сумматоре.

Сумматор – операционный узел ЭВМ, выполняющий арифметическое суммирование кодов чисел. Сложение происходит поразрядно. Выделяют полусумматор и полный сумматор.

Обозначения:

S – Результат; C – бит переноса; a,b – входные операнды.

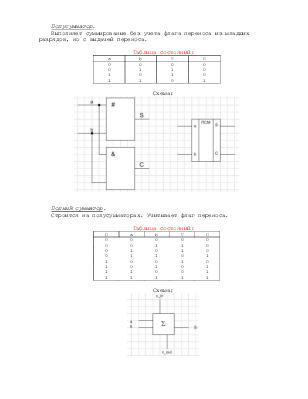

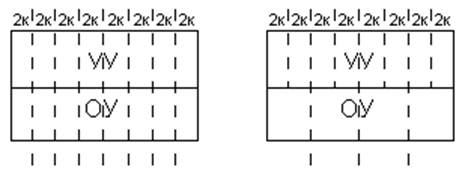

Полусумматор.

Выполняет суммирование без учета флага переноса из младших разрядов, но с выдачей переноса.

Таблица состояний:

|

a |

b |

S |

C |

|

0 |

0 |

0 |

0 |

|

0 |

1 |

1 |

0 |

|

1 |

0 |

1 |

0 |

|

1 |

1 |

0 |

1 |

Схема:

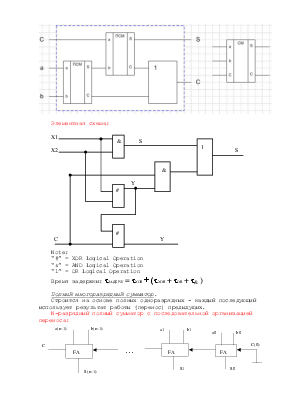

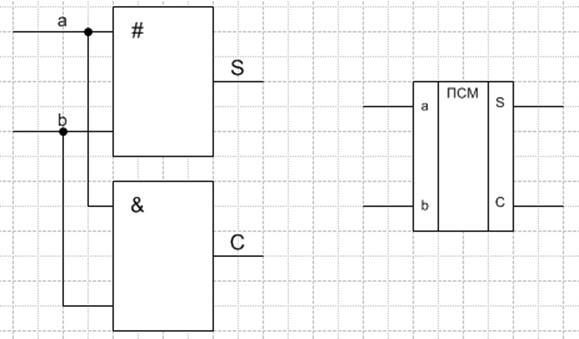

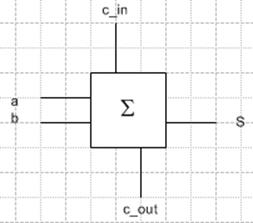

Полный сумматор.

Строится на полусумматорах. Учитывает флаг переноса.

Таблица состояний:

|

С |

a |

b |

S |

C |

|

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

1 |

0 |

|

0 |

1 |

0 |

1 |

0 |

|

0 |

1 |

1 |

0 |

1 |

|

1 |

0 |

0 |

1 |

0 |

|

1 |

0 |

1 |

0 |

1 |

|

1 |

1 |

0 |

0 |

1 |

|

1 |

1 |

1 |

1 |

1 |

Схема:

Элементная схема:

Note:

“#” = XOR Logical Operation

“&” = AND Logical Operation

“1” = OR Logical Operation

Время задержки: τЗАДЕРЖ = τXOR + (τXOR + τOR + τ& )

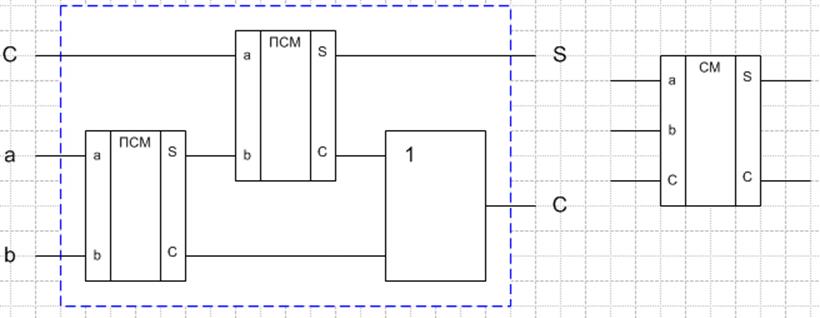

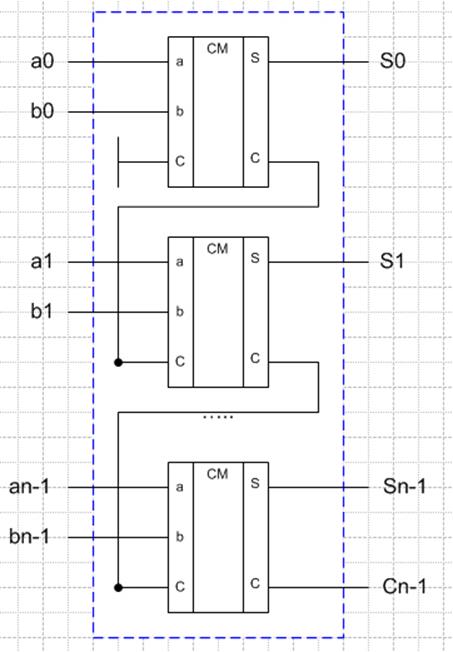

Полный многоразрядный сумматор.

Строится на основе полных одноразрядных - каждый последующий использует результат работы (перенос) предыдущих.

|

Схема:

Достоинство: простота построения.

Недостаток: невысокое быстродействие (задержки велики).

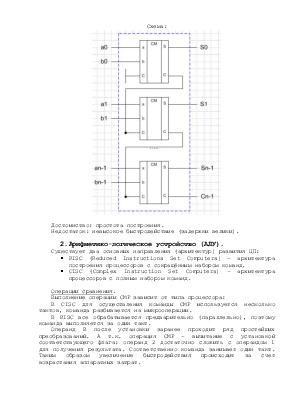

2. Арифметико-логическое устройство (АЛУ).

Существует два основных направления (архитектур) развития ЦП:

§ RISC (Reduced Instructions Set Computers) – архитектура построения процессоров с сокращённым набором команд.

§ CISC (Complex Instruction Set Computers) – архитектура процессоров с полным набором команд.

Операции сравнения.

Выполнение операции CMP зависит от типа процессора:

В CISC для осуществления команды СМР используется несколько тактов, команда разбивается на микрооперации.

В RISC все обрабатывается предварительно (параллельно), поэтому команда выполняется за один такт.

Операнд B после установки заранее проходит ряд простейших преобразований. А т.к. операция CMP – вычитание с установкой соответствующего флага: операнд 2 достаточно сложить с операндом 1 для получения результата. Соответственно команда занимает один такт. Таким образом увеличение быстродействия происходит за счет возрастания аппаратных затрат.

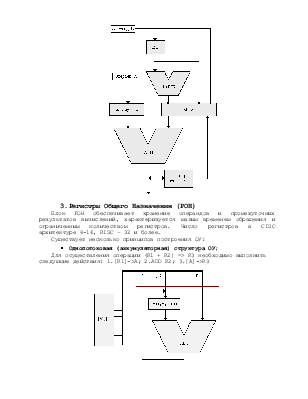

3. Регистры Общего Назначения (РОН)

Блок РОН обеспечивает хранение операндов и промежуточных результатов вычислений, характеризуется малым временем обращения и ограниченным количеством регистров. Число регистров в CISC архитектуре 8-16, RISC – 32 и более.

Существует несколько принципов построения ОУ:

§ Однопотоковая (аккумуляторная) структура ОУ;

Для осуществления операции (R1 + R2) => R3 необходимо выполнить следующие действия: 1.[R1]->A; 2.ADD R2; 3.[A]->R3

Достоинство: простота построения.

Недостаток: невеликое быстродействие.

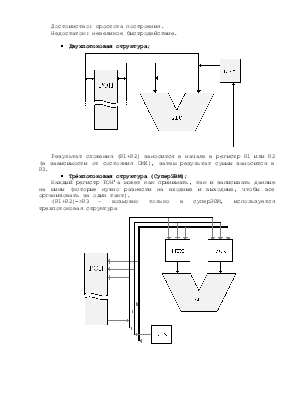

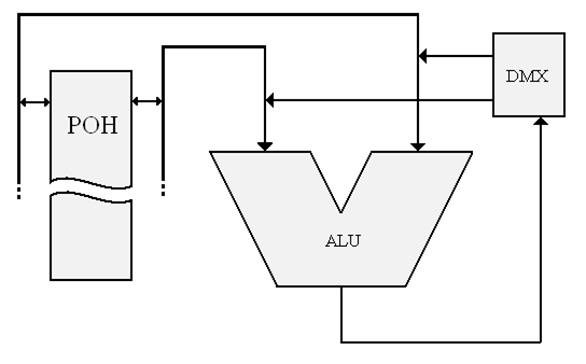

§ Двухпотоковая структура;

Результат сложения (R1+R2) заносится в начале в регистр R1 или R2 (в зависимости от состояния DMX), затем результат суммы заносится в R3.

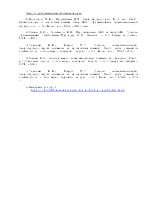

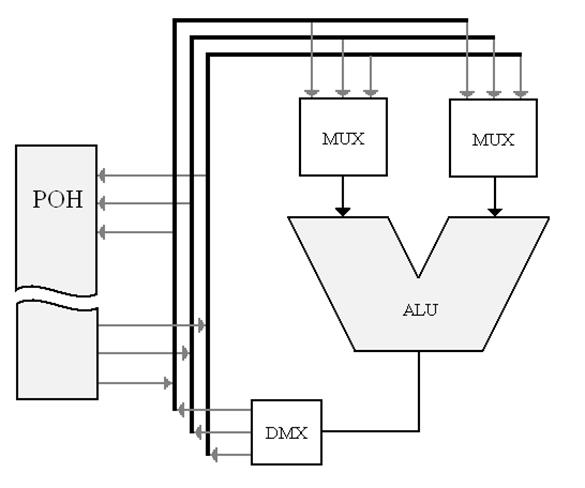

§ Трёхпотоковая структура (СуперЭВМ);

Каждый регистр РОН’а может как принимать, так и записывать данные на шины (которые нужно разнести на входные и выходные, чтобы все организовать за один такт).

(R1+R2)->R3 – возможно только в суперЭВМ, используется трехпотоковая структура

Список дополнительной литературы:

1.Нестеров П.В., Преснухин Д.Л. Микропроцессоры: В 3 кн. Кн.1. Архитектура в проектировании микроЭВМ. Организация вычислительных процессов. – М.:Высш. шк.,1986.-414с.:ил.

2.Мячев А.А., Степанов В.Н. Персональные ЭВМ и микроЭВМ. Основы организации: Справочник/Под ред. А.А. Мячева. - М.: Радио и связь, 1991.-320с.

3.Стрыгин В.В., Щарев Л.С. Основы вычислительной, микропроцессорной техники и программирования: Учеб. для учащихся техникумов. - 2-е изд., перераб. и доп. - М.: Высш. шк., 1989.-479с.

4.Каган Б.М. Электронные вычислительные машины и системы: Учеб. пособие для вузов. - 3-е изд., перераб. и доп. - М.: Энергоатомиздат, 1991.-592с.

5.Стрыгин В.В., Щарев Л.С. Основы вычислительной, микропроцессорной техники и программирования: Учеб. для учащихся техникумов. - 2-е изд., перераб. и доп. - М.: Высш. шк., 1989. - 479 с.

6.Интернет ресурс:

http://dfe3300.karelia.ru/koi/posob/microcpu/index.html

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.