Министерство образования Российской Федерации

Кафедра “Вычислительная техника”

Расчетно-графическая работа № 3

по курсу “микропроцессорные устройства”

Тема: Реализация приорететного контроллера

Выполнили: студенты гр. ВМ-82

Коломеец А.Н.

Толстых Д.Л.

Проверил: ст. преподаватель

Бурдинский И.Н.

Хабаровск 2002

Техническое задание

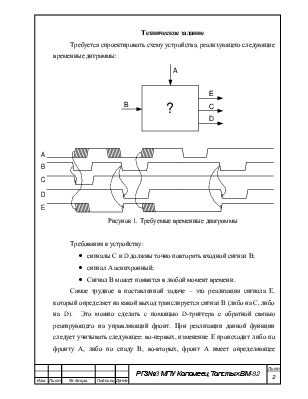

Требуется спроектировать схему устройства, реализующего следующие временные диграммы:

Рисунок 1. Требуемые временные диаграммы

Требования к устройству:

· сигналы С и D должны точно повторять входной сигнал В;

· сигнал А асинхронный;

· Сигнал В может появится в любой момент времени.

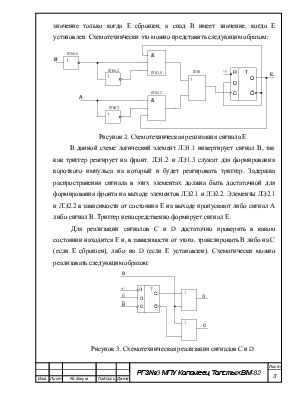

Самое трудное в поставленной задаче – это реализация сигнала Е, который определяет на какой выход транслируется сигнал В (либо на С, либо на D). Это можно сделать с помощью D-триггера с обратной связью реагирующего на управляющий фронт. При реализации данной функции следует учитывать следующее: во-первых, изменение Е происходит либо по фронту А, либо по спаду В, во-вторых, фронт А имеет определяющее значение только когда Е сброшен, а спад В имеет значение, когда Е установлен. Схемотехнически это можно представить следующим образом:

Рисунок 2. Схемотехническая реализация сигнала Е

В данной схеме логический элемент ЛЭ1.1 инвертирует сигнал В, так как триггер реагирует на фронт. ЛЭ1.2 и ЛЭ1.3 служат для формирования короткого импульса на который и будет реагировать триггер. Задержка распространения сигнала в этих элементах должна быть достаточной для формирования фронта на выходе элементов ЛЭ2.1 и ЛЭ2.2. Элементы ЛЭ2.1 и ЛЭ2.2 в зависимости от состояния Е на выходе пропускают либо сигнал А либо сигнал В. Триггер непосредственно формирует сигнал Е.

Для реализации сигналов С и D достаточно проверять в каком состоянии находится Е и, в зависимости от этого, транслировать В либо на С (если Е сброшен), либо на D (если Е установлен). Схематически можно реализовать следующим образом:

Рисунок 3. Схемотехническая реализация сигналов С и D

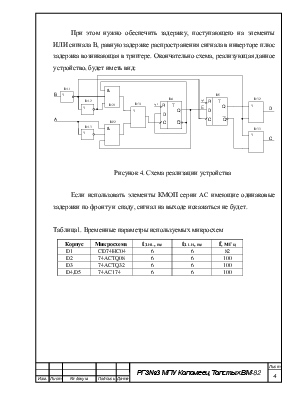

При этом нужно обеспечить задержку, поступающего на элементы ИЛИ сигнала В, равную задержке распространения сигнала в инверторе плюс задержка возникающая в триггере. Окончательно схема, реализующая данное устройство, будет иметь вид:

Рисунок 4. Схема реализации устройства

Если использовать элементы КМОП серии AC имеющие одинаковые задержки по фронту и спаду, сигнал на выходе искажаться не будет.

Таблица1. Временные параметры используемых микросхем

|

Корпус |

Микросхема |

tз HL, нс |

tз LH, нс |

f, МГц |

|

D1 |

CD74HC04 |

6 |

6 |

82 |

|

D2 |

74ACTQ08 |

6 |

6 |

100 |

|

D3 |

74ACTQ32 |

6 |

6 |

100 |

|

D4,D5 |

74AC174 |

6 |

6 |

100 |

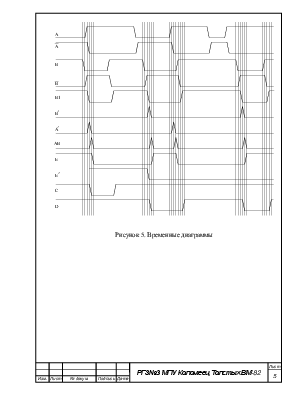

Рисунок 5. Временные диаграммы

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.