Министерство образования Российской Федерации

Кафедра “Вычислительная техника”

Расчётно-графическая работа №2

по курсу “микропроцессорные устройства”

Выполнили: студенты гр. ВМ-82

Коломеец А.Н.

Толстых Д.Л.

Проверил: ст. преподаватель

Бурдинский И.Н.

Хабаровск 2002

Техническое задание

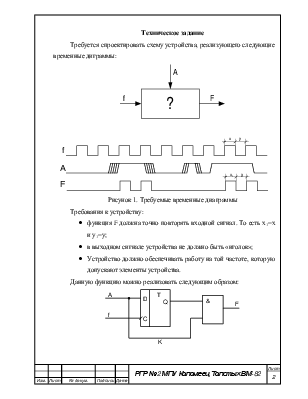

Требуется спроектировать схему устройства, реализующего следующие временные диграммы:

Рисунок 1. Требуемые временные диаграммы

Требования к устройству:

· функция F должна точно повторять входной сигнал. То есть х1=х и у1=у;

· в выходном сигнале устройства не должно быть «иголок»;

· Устройство должно обеспечивать работу на той частоте, которую допускают элементы устройства.

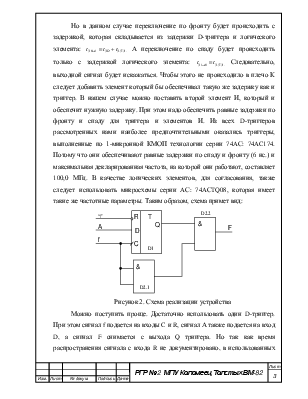

Данную функцию можно реализовать следующим образом:

Но в данном случае переключение по фронту

будет происходить с задержкой, которая складывается из задержки D-триггера и логического элемента: ![]() А

переключение по спаду будет происходить только с задержкой логического

элемента:

А

переключение по спаду будет происходить только с задержкой логического

элемента: ![]() Следовательно, выходной сигнал будет

искажаться. Чтобы этого не происходило в плечо К следует добавить элемент

который бы обеспечивал такую же задержку как и триггер. В нашем случае можно

поставить второй элемент И, который и обеспечит нужную задержку. При этом надо

обеспечить равные задержки по фронту и спаду для триггера и элементов И. Из

всех D-триггеров рассмотренных нами наиболее

предпочтительными оказались триггеры, выполненные по 1-микронной КМОП

технологии серии 74AС: 74AC174.

Потому что они обеспечивают равные задержки по спаду и фронту (6 нс.) и

максимальная декларированная частота, на которой они работают, составляет 100,0

МГц. В качестве логических элементов, для согласования, также следует

использовать микросхемы серии AС: 74AСTQ08, которая имеет такие же частотные параметры. Таким

образом, схема примет вид:

Следовательно, выходной сигнал будет

искажаться. Чтобы этого не происходило в плечо К следует добавить элемент

который бы обеспечивал такую же задержку как и триггер. В нашем случае можно

поставить второй элемент И, который и обеспечит нужную задержку. При этом надо

обеспечить равные задержки по фронту и спаду для триггера и элементов И. Из

всех D-триггеров рассмотренных нами наиболее

предпочтительными оказались триггеры, выполненные по 1-микронной КМОП

технологии серии 74AС: 74AC174.

Потому что они обеспечивают равные задержки по спаду и фронту (6 нс.) и

максимальная декларированная частота, на которой они работают, составляет 100,0

МГц. В качестве логических элементов, для согласования, также следует

использовать микросхемы серии AС: 74AСTQ08, которая имеет такие же частотные параметры. Таким

образом, схема примет вид:

Рисунок 2. Схема реализации устройства

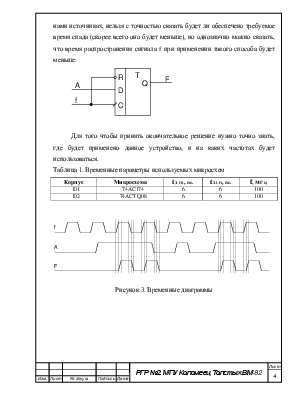

Можно поступить проще. Достаточно использовать один D-триггер. При этом сигнал f подается на входы C и R, сигнал А также подается на вход D, а сигнал F снимается с выхода Q триггера. Но так как время распространения сигнала с входа R не документировано, в использованных нами источниках, нельзя с точностью сказать будет ли обеспечено требуемое время спада (скорее всего оно будет меньше), но однозначно можно сказать, что время распространения сигнала f при применении такого способа будет меньше:

Для того чтобы принять окончательное решение нужно точно знать, где будет применено данное устройство, и на каких частотах будет использоваться.

Таблица 1. Временные параметры используемых микросхем

|

Корпус |

Микросхема |

tз HL, нс. |

tз LH, нс. |

f, МГц |

|

D1 |

74AC174 |

6 |

6 |

100 |

|

D2 |

74ACTQ08 |

6 |

6 |

100 |

Рисунок 3. Временные диаграммы

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.