включения/выключения в зависимости от того, является ли полученный текст зашифрованным или нет. Для этого использовать в тексте определенную метку, наличие которой предупреждает о том, что по линии передается зашифрованный текст.

Для обеспечения связи с компьютером нужно предусмотреть схему работы по шине ISA, выдачу и прием информации.

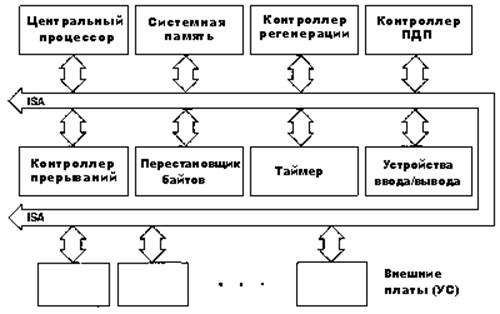

Структура персонального компьютера типа IBM PC с точки зрения разработчика устройств сопряжения (УС), ориентированных на ISA, может быть условно представлена в виде рисунка:

Помимо

центрального процессора, системной памяти (оперативной и постоянной),

стандартных средств ввода/вывода, входящих в любую микропроцессорную систему,

здесь следует отдельно выделить встроенные контроллеры прерываний и прямого

доступа к памяти (ПДП), перестановщик байтов данных, программируемый таймер и

контроллер регенерации памяти. Все эти устройства, расположенные на материнской

(системной) плате (motherboard) компьютера или вставленные в слоты ISA

(устройства ввода/вывода), участвуют в обмене по магистрали и могут быть

использованы разрабатываемыми УС.

Помимо

центрального процессора, системной памяти (оперативной и постоянной),

стандартных средств ввода/вывода, входящих в любую микропроцессорную систему,

здесь следует отдельно выделить встроенные контроллеры прерываний и прямого

доступа к памяти (ПДП), перестановщик байтов данных, программируемый таймер и

контроллер регенерации памяти. Все эти устройства, расположенные на материнской

(системной) плате (motherboard) компьютера или вставленные в слоты ISA

(устройства ввода/вывода), участвуют в обмене по магистрали и могут быть

использованы разрабатываемыми УС.

Задатчиками (хозяевами) шины могут выступать центральный процессор (самая обычная ситуация), контроллер ПДП, контроллер регенерации и некоторые внешние платы. В каждом цикле обмена задатчиком всегда является только одно устройство. Контроллер ПДП захватывает магистраль (запрещает работу центрального процессора) на время прямой передачи информации между устройством ввода/вывода и памятью (по запросу устройства ввода/вывода). Контроллер регенерации периодически становится задатчиком магистрали для проведения циклов регенерации системной динамической памяти через заданные интервалы времени.

Магистраль ISA относится к демультиплексированным (то есть имеющим раздельные шины адреса и данных) 16-разрядным системным магистралям среднего быстродействия. Обмен осуществляется 8- или 16-разрядными данными. На магистрали реализован раздельный доступ к памяти компьютера и к устройствам ввода/вывода (для этого имеются специальные сигналы). Максимальный объем адресуемой памяти составляет 16 Мбайт (24 адресные линии). Максимальное адресное пространство для устройств ввода/вывода - 64 Кбайта (16 адресных линий), хотя практически все выпускаемые платы расширения используют только 10 адресных линий (1 Кбайт). Магистраль поддерживает регенерацию динамической памяти, радиальные прерывания и прямой доступ к памяти.

4.1.Техническое задание

В процессе выполнения курсового проекта необходимо разработать систему, реализующую простой криптографический алгоритм в рельном режиме времени и реализовать её в виде аппаратного комплекса.

Требования:

1. чтение с параллельного порта текстовой последовательности ASCII символов разрядностью 64 бита;

2. отправка на параллельный порт текстовой последовательности ASCII символов разрядностью 64 бита, представляющей собой закодированную входную

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.