Санкт-Петербургский Государственный Политехнический Университет

Факультет Технической Кибернетики

Кафедра Автоматики и Вычислительной Техники

Лабораторная работа №1

По предмету:

«Организация Микропроцессоров»

Тема:

«Секционные микропроцессоры

с микропрограммным управлением серии К1804»

Студент гр. 3081/5 Силантьев С.А.

Преподаватели: Павловский Е.Г.

Жвариков В.А.

Санкт-Петербург

2006

1. Цель работы

Практическое ознакомление с основными модулями микропроцессорного комплекта серии К1804, организацией и методикой построения МП-устройств на его основе, приобретение навыков программирования микропроцессоров данного класса.

2. Структурная схема микротренажера МТ1804.

(Рис. 1)

Структурная схема тренажера содержит:

§ блок центрального процессора, включающий центральный процессорный элемент К1804ВС1, регистр состояния с выходным коммутатором-мультиплексором флагов признаков, мультиплексоры сдвига и регистр выходных данных К1804ИР1;

§ блок микропрограммного управления, включающий БИС управления адресом микрокоманд К1804ВУ1, ЗУМК емкостью в шестнадцать 32-разрядных слов, 32-разрядный регистр микрокоманд, устройство управления выборкой следующего адреса;

§ устройство ввода информации: клавишные переключатели адреса, данных и других элементов управления;

§ устройство вывода информации: набор светодиодных индикаторов;

§ переключатели управления;

3.Схема ЦПЭ К1804ВС1.

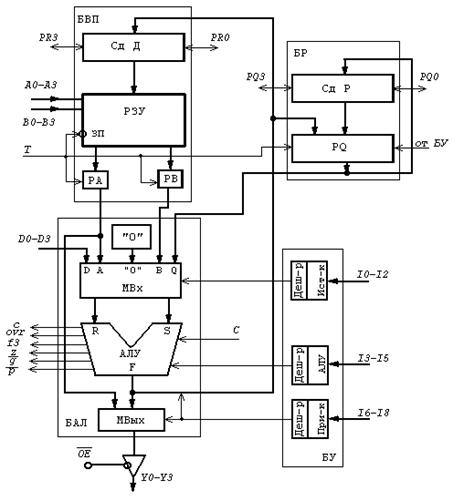

(Рис. 2)

ЦПЭ предназначен для арифметико-логической обработки данных и временного хранения исходных данных и результатов вычислений во встроенной регистровой памяти.

На схеме можно выделить следующие 4 крупные структурные единицы:

1. блок внутренней памяти (БВП),

2. блок арифметико-логический (БАЛ),

3. блок регистра Q (БР),

4. блок управления (БУ).

1. Блок внутренней памяти содержит:

-4-разрядное запоминающее устройство (РЗУ),

-сдвигатель данных (СдД),

-два 4-разрядных регистра РА и РВ.

2. Блок арифметико-логический включает:

-двухвходовое АЛУ,

-мультиплексор входных данных (МВх),

-мультиплексор выходных данных (МВых),

-лог “0”, для подачи на один из входов нулевого значения.

3. Блок регистра Q состоит из:

-дополнительного (рабочего) регистра PQ,

-сдвигателя регистра (СдР).

4. Блок управления формирует управляющие сигналы для остальных блоков МП.

4. Секции управления адресом микрокоманды К1804ВУ1

(Рис.3 Структурная схема СУАМ К1804ВУ1)

Основным назначением секции управления адресом микрокоманды (СУАМ) является формирование адреса следующей микрокоманды. Источником адреса микрокоманд могут быть как внутренние блоки СУАМ, так и внешние формирователи адреса микрокоманд. К внутренним блокам относятся счетчик микрокоманд, обеспечивающий последовательное считывание команд, и стек, в котором запоминаются адреса возврата при работе с подпрограммами. Внешними источниками адреса являются регистр микрокоманд (его адресная часть) и преобразователи начального адреса микропрограмм команд и векторов прерываний. Источник адреса в СУАМ выбирается с помощью четырехвходового мультиплексора. Источником адреса могут быть стек, счетчик микрокоманд , адресная информация, поступающая на входы СУАМ D0-D3 либо регистр адреса.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.