|

“tx_control.vhd” |

|

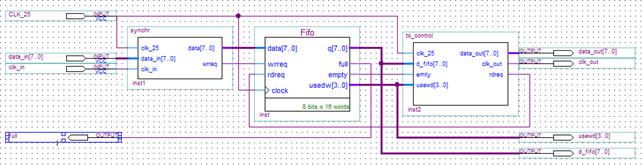

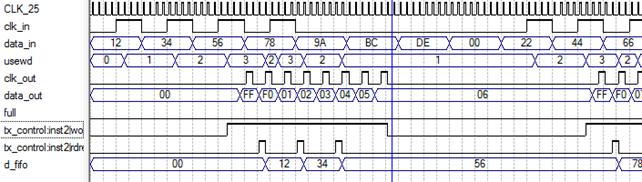

library IEEE; use IEEE.std_logic_1164.all; entity tx_control is port( clk_25 : in std_logic; d_fifo : in std_logic_vector (7 downto 0); emty : in std_logic; usewd : in integer range 15 downto 0; data_out : out std_logic_vector (7 downto 0); clk_out : out std_logic; rdreq : out std_logic ); end tx_control; architecture RTL of tx_control is signal tmp_clk : std_logic; signal work_send : bit := '0'; begin process (clk_25, usewd) variable c_c : integer range 63 downto 0 := 0; begin if usewd = 0 then work_send <= '0'; elsif usewd >= 3 then work_send <= '1'; elsif c_c = 25 then work_send <= '0'; end if; if clk_25'event and clk_25 = '1' and (work_send = '1' or c_c = 25) then if c_c = 0 then rdreq <= '0'; clk_out <= '0'; elsif c_c = 1 then rdreq <= '0'; clk_out <= '0'; data_out <= "11111111"; elsif c_c = 4 then rdreq <= '1'; clk_out <= '0'; data_out <= "11110000"; elsif c_c = 7 or c_c = 13 or c_c = 19 then rdreq <= '0'; clk_out <= '0'; data_out <= "0000" & d_fifo(7 downto 4); elsif c_c = 10 or c_c = 16 then rdreq <= '1'; clk_out <= '0'; data_out <= "0000" & d_fifo(3 downto 0); elsif c_c = 22 then rdreq <= '0'; clk_out <= '0'; data_out <= "0000" & d_fifo(3 downto 0); elsif c_c = 2 or c_c = 5 or c_c = 8 or c_c =11 or c_c = 14 or c_c = 17 or c_c = 20 or c_c = 23 then rdreq <= '0'; clk_out <= '1'; elsif c_c = 25 then rdreq <= '0'; clk_out <= '0'; c_c := 0; else rdreq <= '0'; clk_out <= '0'; end if; c_c := c_c + 1; end if; end process; end RTL; |

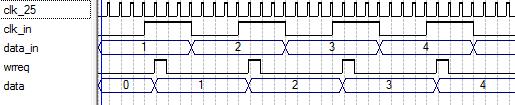

Блок tx_control организовывает формирование пакетов определенного формата и необходимой длинны, а так же формирует сигнал тактирования для выходных данных.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.