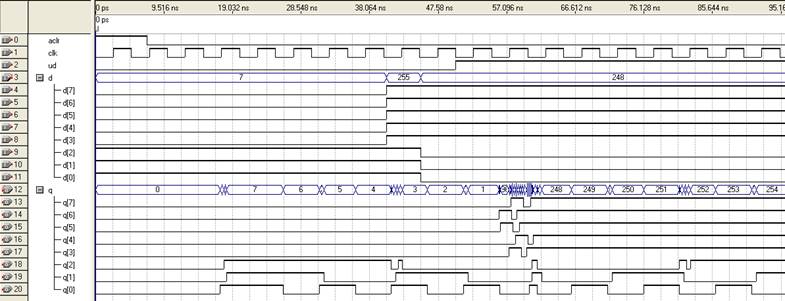

Из временной диаграммы видно, что асинхронная загрузка является менее эффективной, чем синхронная, т.к. присутствует большое количество рисков сбоя.

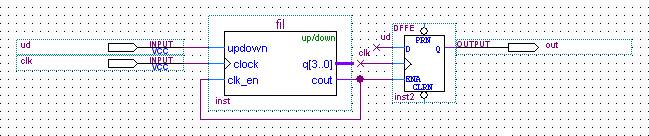

Рис. 14. Принципиальная схема устройства фильтрации коротких импульсов.

clk_en – вход разрешения синхронизации; разрешает все синхронные операции

Рис. 15. Диаграмма работы устройства фильтрации коротких импульсов.

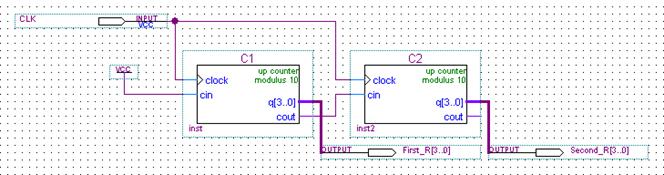

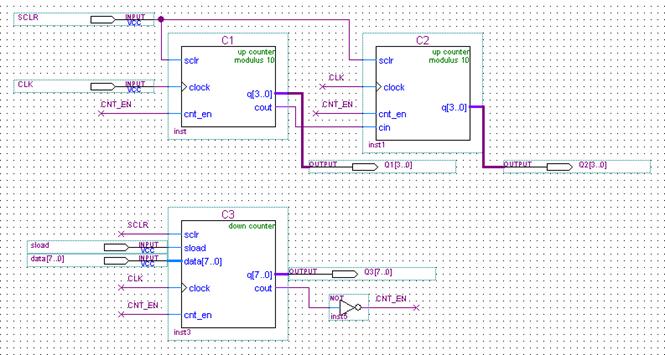

Рис. 16. Принципиальная схема двухтетрадного двоично-десятичного счетчика.

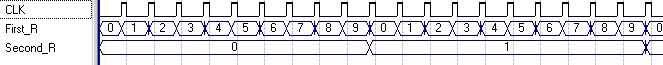

На вход C1.cin подаётся разрешение счёта, выход C1.cout подается на вход C2.cin. First_R – младший разряд, Second_R – старший разряд.

Рис. 17. Диаграмма работы двухтетрадного двоично-десятичного счетчика.

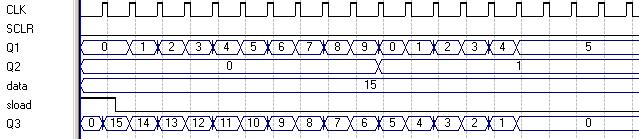

Рис. 18. Принципиальная схема преобразователя двоичного кода в двоично-десятичный код.

Двоично-десятичный счетчик устанавливается в "0", загружается двоичное число и подаются счетные импульсы на вход вычитания двоичного счетчика и на вход сложения двоично-десятичного.

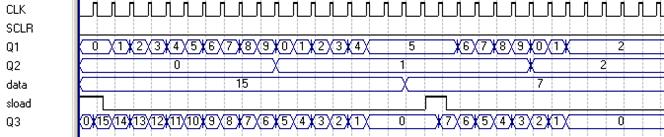

Рис. 19. Диаграмма работы преобразователя двоичного кода в двоично-десятичный код.

Диапазон преобразуемых чисел 0- 99.

Схема накапливающего сумматора совпадает со схемой преобразователя двоичного кода в двоично-дестичный. Следующее слагаемое передается при подаче импульса sload, перед каждым преобразованием не производится сброс счетчика в «0».

Рис. 20. Диаграмма работы накапливающего сумматора.

2. Выводы

Схема делителя частоты на произвольное число

Схема делителя была синтезирована двумя разными способами, из которых видно, что схема с использованием синхронной загрузки эффективнее.

Схема двухтетрадного двоично-десятичного счётчика

Для синтеза схемы были использованы два счётчика с модулем счёта 10, один из которых отвечал за единицы, а другой – за десятки. Диапазон счёта данного счётчика 0-99.

Схема преобразователя двоичного кода в двоично-десятичный

Для синтеза схемы были использованы двухтетрадный двоично-десятичный счётчик на сложение и двоичный 8-разрядный счётчик на вычитание. Запрещением к счёту служил сигнал с выхода 8-разрядного счётчика.

Схема накапливающего сумматора

В данной схеме производится последовательное преобразование двоичного кода в двоично-десятичный без сброса в "0" после каждого преобразования. Слагаемые подаются на вход Data 8-разрядного счётчика с подачей импульса на входа Load. Частота подачи слагаемых при неизвестном значении предыдущего слагаемого должна быть в 100 раз меньше подаваемых тактовых сигналов. Диапазон конечной суммы 0 – 99.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.