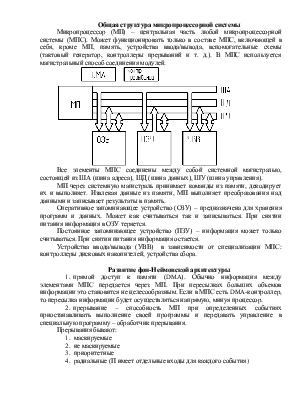

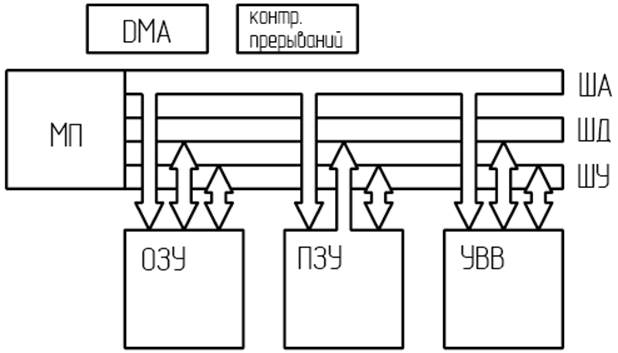

Общая структура микропроцессорной системы

Микропроцессор (МП) – центральная часть любой микропроцессорной системы (МПС). Может функционировать только в составе МПС, включающей в себя, кроме МП, память, устройства ввода/вывода, вспомогательные схемы (тактовый генератор, контроллеры прерываний и т. д.). В МПС используется магистральный способ соединения модулей.

Все элементы МПС соединены между собой системной магистралью, состоящей из ША (шина адреса), ШД (шина данных), ШУ (шина управления).

МП через системную магистраль принимает команды из памяти, декодирует их и выполняет. Извлекая данные из памяти, МП выполняет преобразования над данными и записывает результаты в память.

Оперативное запоминающее устройство (ОЗУ) – предназначена для хранения программ и данных. Может как считываться так и записываться. При снятии питания информация в ОЗУ теряется.

Постоянное запоминающее устройство (ПЗУ) – информация может только считываться. При снятии питания информация остается.

Устройства ввода/вывода (УВВ) в зависимости от специализации МПС: контроллеры дисковых накопителей, устройства сбора.

Развитие фон-Неймовской архитектуры

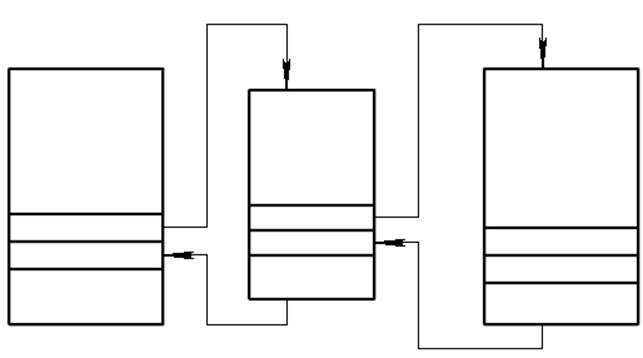

1. прямой доступ к памяти (DMA). Обычно информация между элементами МПС передается через МП. При пересылках больших объемов информации это становится не целесообразным. Если в МПС есть DMA-контроллер, то пересылка информации будет осуществляться напрямую, минуя процессор.

2. прерывание – способность МП при определенных событиях приостанавливать выполнение своей программы и передавать управление в специальную программу – обработчик прерывания.

Прерывания бывают:

1. маскируемые

2. не маскируемые

3. приоритетные

4. радиальные (П имеет отдельные входы для каждого события)

5. векторные (П имеет только один вход запросов прерывания)

Устройство процессора

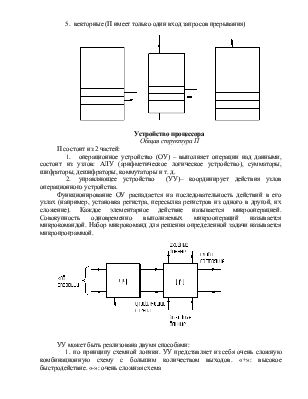

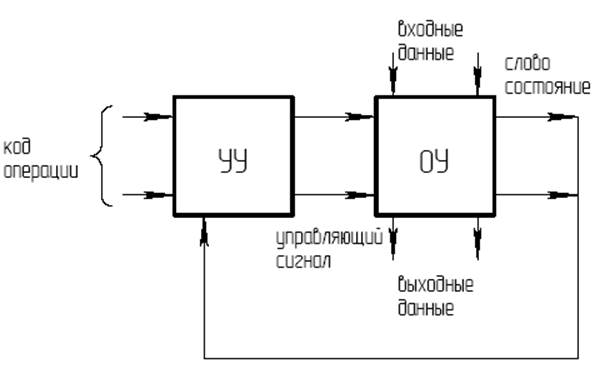

Общая структура П

П состоит из 2 частей:

1. операционное устройство (ОУ) – выполняет операции над данными, состоит из узлов: АЛУ (арифметическое логическое устройство), сумматоры, шифраторы, дешифраторы, коммутаторы и т. д.

2. управляющее устройство (УУ)– координирует действия узлов операционного устройства.

Функционирование ОУ распадается на последовательность действий в его узлах (например, установка регистра, пересылка регистров из одного в другой, их сложение). Каждое элементарное действие называется микрооперацией. Совокупность одновременно выполняемых микроопераций называется микрокомандой. Набор микрокоманд для решения определенной задачи называется микропрограммой.

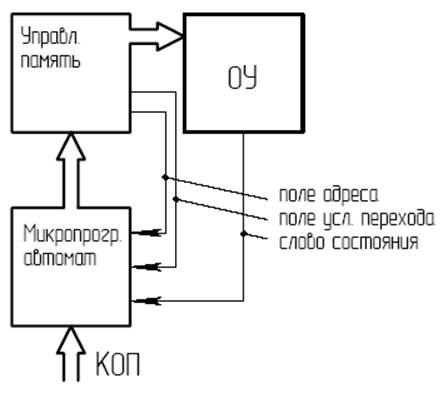

УУ может быть реализована двумя способами:

1. по принципу схемной логики. УУ представляет из себя очень сложную комбинационную схему с большим количеством выходов. «+»: высокое быстродействие. «-»: очень сложная схема

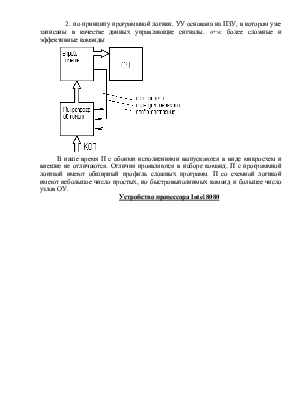

2. по принципу программной логики. УУ основана на ПЗУ, в котором уже записаны в качестве данных управляющие сигналы. «+»: более сложные и эффективные команды

В наше время П с обоими исполнениями выпускаются в виде микросхем и внешне не отличаются. Отличия проявляются в наборе команд. П с программной логикой имеют обширный профиль сложных программ. П со схемной логикой имеют небольшое число простых, но быстровыполнимых команд и большее число узлов ОУ.

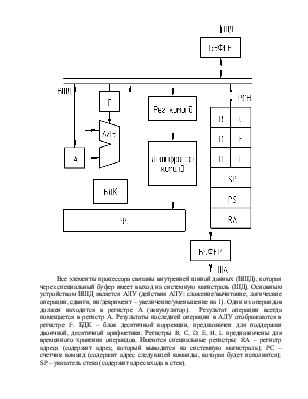

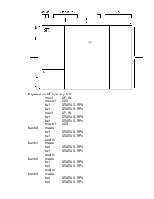

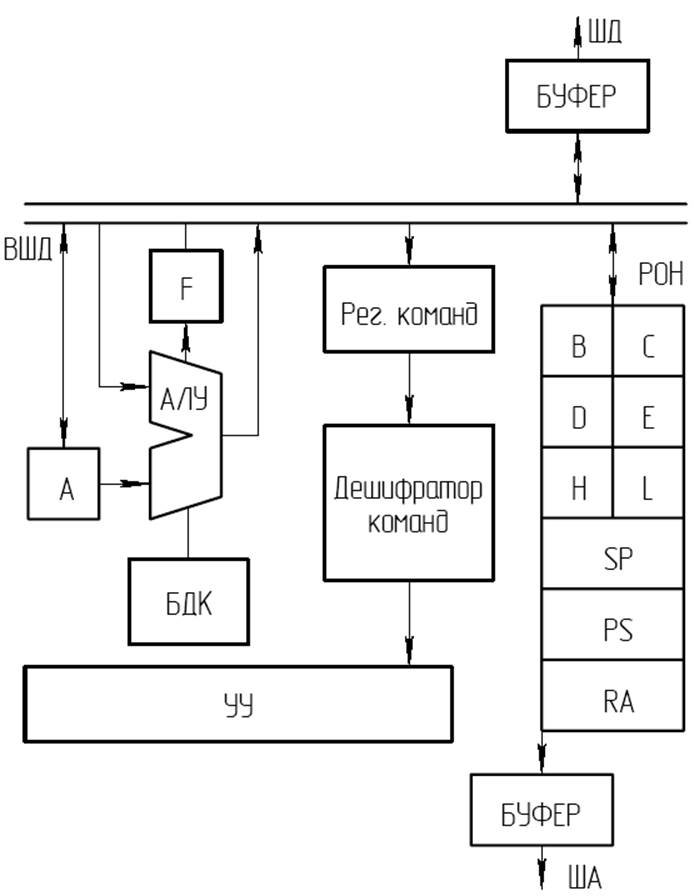

Устройство процессора Intel 8080

Все элементы процессора связаны внутренней шиной данных (ВШД), которая через специальный буфер имеет выход на системную магистраль (ШД). Основным устройством ВШД является АЛУ (действия АЛУ: сложение/вычитание, логические операции, сдвиги, ин/декримент – увеличение/уменьшение на 1). Один из операндов должен находится в регистре А (аккумулятор). Результат операции всегда помещается в регистр А. Результаты последней операции в АЛУ отображаются в регистре F. БДК – блок десятичной коррекции, предназначен для поддержки двоичной, десятичной арифметики. Регистры B, C, D, E, H, L предназначены для временного хранения операндов. Имеются специальные регистры: RA – регистр адреса (содержит адрес, который выводится на системную магистраль); PC – счетчик команд (содержит адрес следующей команды, которая будет исполнятся); SP – указатель стека (содержит адрес входа в стек).

Стек – память, с упрощенной формой адресации. Использует принцип «первым вошел, последним вышел».

УУ состоит из регистра команды, в который поступает код команды из памяти, дешифратора команд и шифратора машинных циклов (микропрограммный аппарат) и управляющей памяти.

Работа П определяется кодом команды и синхронизируется тактовыми сигналами. Период тактовых сигналов называется машинным тактом. Машинный цикл – время требуемое для извлечения одного байта информации или выполнения команды определяемой одним логическим словом. Командный цикл – время выполнения команды, извлечения команды и ее декодирования, может занимать от 1 до 5 машинных циклов.

Для Intel 8080 существует 10 типов машинных циклов:

1. Извлечение кода команды;

2. Извлечение данных из памяти;

3. Запись данных в память;

4. Извлечение данных из внешнего устройства;

5. Запись данных на внешнее устройство;

6. Извлечение информации из стека

7. Ввод в стек

8. Обслуживание прерывания

9. Остановка

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.