Логічна сума в перших дужках також реалізується з допомогою мульти-плексора 4:1, якщо на адресні входи його пдати змінні х0 та х4. Принципова схема, що реалізує розглядаєму логічну функцію, приведена на рис.3.10.

Але така схема являється лише прикладом і приктично не реалізуєма, так як в серіях мікросхем відсутні мультиплексори 4:1, а спарений мультиплексор К1533КП2 має об’єднані адресні входи. Практично задача може бути розв’язана при використанні мультиплексора 8:1.

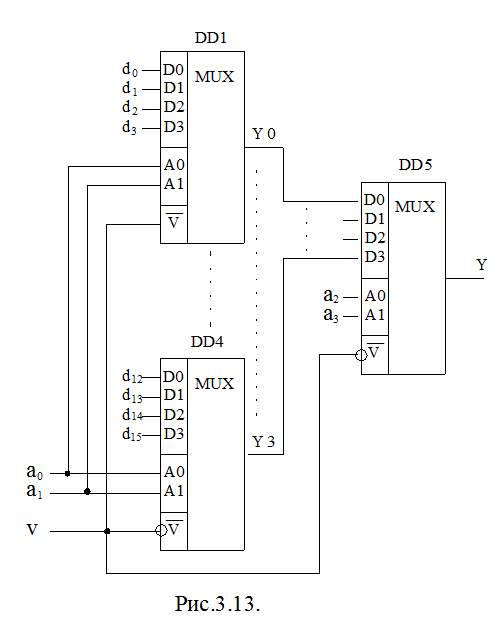

|

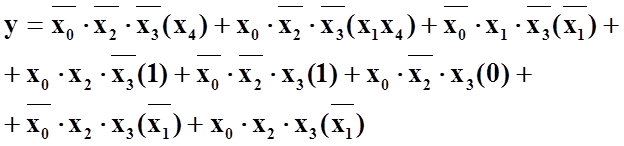

В табл.3.2 зведені значення необхідних сигналів, які подаються на відповідні інформаційні входи. На рис.3.11. приведена схема, що реалізує розглядаєму функцію на

Табл.3.2.

x3 |

x2 |

x0 |

Di-

|

|

0 |

0 |

0 |

x4 |

|

0 |

0 |

1 |

x1x4 |

|

|

1 |

0 |

x1 |

|

0 |

1 |

1 |

1 |

|

1 |

0 |

0 |

1 |

|

1 |

0 |

1 |

0 |

|

|

1 |

0 |

x1 |

|

|

1 |

1 |

x1 |

мультиплексорі К1533КП7. Необхідні допоміжні логічні функції реалізуються з використанням одного корпуса мікросхеми К1533 ЛА3.

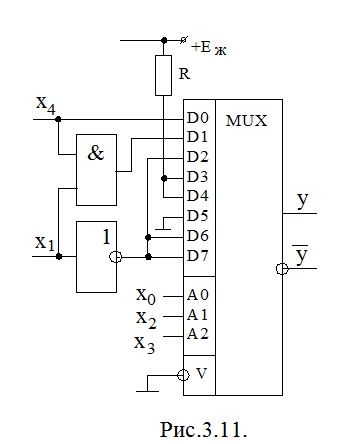

В більшості серій мікросхем мультиплексори, виготовляємі в

вигляді самостійних виробів, мають кількість інформаційних входів, що не

перевищує 16. Збільшення їх кількості досягається різними прийомами зєднання

окремих мультиплексорів. На рис. 3.12. прниведена схема паралельного

нарощування.

В любій схемі для розширення кількості входів необхідно пвдвищувати кількість адресних провідників (ємність адресного простору, адресної шини). В схемі, приведеній на рис.3.12. розширення адресного простору досягається викрористанням входу V , який , об’єднаний в обох мультиплексорах через інвертор, являється старшим розрядом адресної шини. При а2 =0 зміна сигналів на а0,а1 дозволить вибирати входи d0 –d3 шини даних і через елемент АБО (DD4) передавати на вихід Y. Мультиплексор DD2 при цьому відключений високим рівнем сигналу на виході DD3. При а2=1 зміною а0,а1 забезпечується комутація входів d4 – d7 на вихід Y . При наявності в мультиплексорах інверсних виходів , їх обєднання забезпечується елементом І-НІ(DD5).

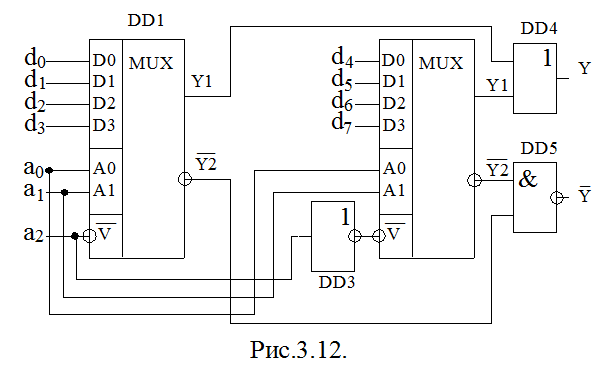

При

необхідності суттє-вого нарощування кількості комутуємих інформаційних входів

використовується пірамідальний спосіб наро-щування. Приклад його реалізації

приведений на рис. 3.13. Ця схема в реалізації являється більш гнучкою. Адресні

входи мультиплек-сорів нижчого рівня DD1-DD4 об’єднуються паралель-но і являються молодшими

розрядами адресного прос-тору. Їх кількість визнача-ється

тільки вихідною роз-рядністю інформаційних входів кожного мультиплек-сора.

Мультиплексор верх-ньої ступені задає старші розряди адресного простору,

завдяки яким він забезпечує комутацію виходу одного з мультиплексорів Y0 – Y3 на загальний

вихід Y.При  використанні

іншої комбінаційної схемотехніки, наприклад, дешифраторів, про які буде йти

мова нижче, появляються більш широкі можливості нарощування розрядності

інформаційної та адресної шин.

використанні

іншої комбінаційної схемотехніки, наприклад, дешифраторів, про які буде йти

мова нижче, появляються більш широкі можливості нарощування розрядності

інформаційної та адресної шин.

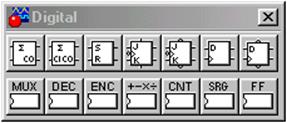

3. Використання пакету EWB для вивчення роботи мультиплексоів

Мультиплексори

в пакету EWB знаходяться в меню DIGIT , опція MUX (Рис. ) з якої можна вибрати досліджуємі мікросхеми як серії SN74. Інформацію про функціонування кожної

конкретної мікросхеми можна отримати з таблиці істинності даної мікросхеми, яка

може бути доступною через підказку HELP. Для отримання більш детальної інформації про використання мікросхем

можна отримати з довідкової літератури. Відсутність зарубіжних довідників

компенсується таблицею відповідності між зарубіжними і вітчизняними

мікросхемами.

Мультиплексори

в пакету EWB знаходяться в меню DIGIT , опція MUX (Рис. ) з якої можна вибрати досліджуємі мікросхеми як серії SN74. Інформацію про функціонування кожної

конкретної мікросхеми можна отримати з таблиці істинності даної мікросхеми, яка

може бути доступною через підказку HELP. Для отримання більш детальної інформації про використання мікросхем

можна отримати з довідкової літератури. Відсутність зарубіжних довідників

компенсується таблицею відповідності між зарубіжними і вітчизняними

мікросхемами.

|

Номер по EWB |

Вітчизн. аналог |

Номер по EWB |

Вітчизн. аналог |

|

74353 |

КП17 |

74158 |

КП18 |

|

74352 |

КП19 |

74157 |

КП16 |

|

74298 |

КП13 |

74153 |

КП2 |

|

74258 |

КП14 |

74151 |

КП7 |

|

74257 |

КП11 |

74139 |

ІД14 |

|

74253 |

КП12 |

74КП150 |

КП1 |

|

74251 |

КП15 |

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.