парності коду на входах І0÷І7 маємо слідуючіі логічні співвідношення між вхідними й вихідними сигналами:

3. Використання пакету EWB для вивчення роботи арифметико-логічних пристроїв, цифрових компараторів та схем контролю парності.

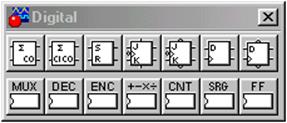

В пакеті EWB

на жаль використовуються лише суматори, які знаходяться знаходяться в меню DIGIT,

опцій, позначених значком

В пакеті EWB

на жаль використовуються лише суматори, які знаходяться знаходяться в меню DIGIT,

опцій, позначених значком ![]() å, а також арифметико-логічний пристрій, що знаходиться в опції, яка

позначена послідовністю слідуючих знаків + - ´ : (Рис.

) Інформацію про функціонування кожної конкретної мікросхеми можна отримати

з таблиці істинності даної мікросхеми, яка може бути доступною через підказку HELP.

Для отримання більш детальної інформації про використання мікросхем можна

отримати з довідкової літератури.

В теоретичній частині практикуму приводяться назви вітчизняних аналогів

мікросхем, що використовуються для виконання арифметичних операцій.

å, а також арифметико-логічний пристрій, що знаходиться в опції, яка

позначена послідовністю слідуючих знаків + - ´ : (Рис.

) Інформацію про функціонування кожної конкретної мікросхеми можна отримати

з таблиці істинності даної мікросхеми, яка може бути доступною через підказку HELP.

Для отримання більш детальної інформації про використання мікросхем можна

отримати з довідкової літератури.

В теоретичній частині практикуму приводяться назви вітчизняних аналогів

мікросхем, що використовуються для виконання арифметичних операцій.

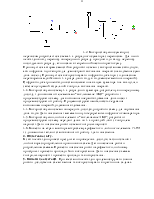

Для дослідження операцій пов’язаних з контролем передачі інформації шляхом контролю парності або непарності передаваємих одиниць , використовуються мікросхеми “виключаюче АБО”, які знаходяться в меню Logic gates ( мікросхеми 4077 і 74266). Умовне позначення логічних елементів приводиться на рис.

4.Порядок виконання роботи.

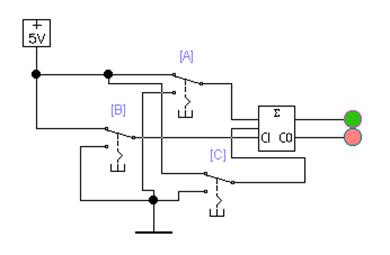

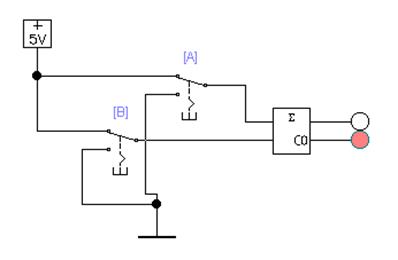

4.1. Досліджуються схеми суматора без переносу і суматора з переносом, які зображені на рис. Для кожної з приведених схем будується таблиця станів, на основі якої складаються аналітичні вирази роботи однорозрядних суматорів.

4.2. Використовуючи суматори з переносом розробляється схема 4-х розрядного суматора з переносом. Для цього необхідно вихід переносу попереднього розряду приєднати до входу переносу послідуючого розряду, як описано в теоретичній частині практикуму. Пропонується авторам самостійно розробити схеми з використанням світодіодів, або цифрових індикаторів для демонстрації виконання операції знаходження суми двох чисел. ( Пропонується використовувати цифрові індикатори з одночасним перетворенням двійкового 4-х розрядного коду в код семисегментних операцій). Цифрові індикатри необхідно встановлювати на входах суматора і на виході, що забезпечує прямий візуальний контроль виконання операції.

4.3. Використовуючи схему 4-х розрядного суматора, розроблену в попередньому досліді, і доповнивши її елементами “виключаюче АБО” розробити і продемонструвати схему для виконання операції віднімання двох чисел і продемонструвати її роботу. Продемонструвати можливість керування виконанням операцій додавання-віднімання.

4.4. Використовуючи схеми попередніх дослідів, розробити схему для порівняння двох кодів. Дати пояснення і математичну інтерпретацію цифрового компаратора.

4.5. Використовуючи логічні елементи “виключаюче АБО”, розробити і продемонструвати схему передачі даних по 4-х провідній лінії з контролем парності. Дати пояснення роботи схеми контролю парності

4.6. Вивести на екран монітора мікросхему арифметико-логічного елемента 74181 і з допомогою таблиці станів вивчити її роботу і дати пояснення.

4. Підготовка звіту.

В звіті необхідно привести результати проведених дослідів, таблиці станів і логічні вирази розроблених принципових схем. Дати пояснення роботи розробленим схемам. Привести пояснення роботи арифметико-логічному пристрою і привести приклади його використання. Дати пояснення схемам контролю парності і привести приклади їх використання.

5. Вимоги до атестації. При атестанції необхідно продемонструвати знання роботи досліджених схем і вміння їх використовувати в практичних

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.