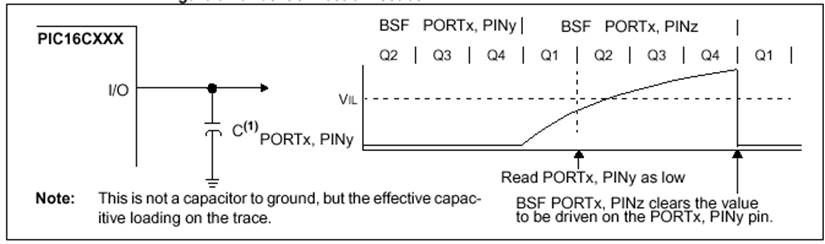

Кращому способом рішення цієї проблеми може бути підключення додаткового резистора до виводу порту. Підключений резистор дозволяє досягти на виводі порту напруги необхідного рівня перед виконанням наступної команди

Використання команд NOP між послідовними звертаннями до регістра PORTX "читання - модифікація запис" є найбільш дешевим але має істотний недолік число команд NOP залежить від значення ємності й тактової частоти мікроконтролера

6.3 Підключення до порту вводу/виводу

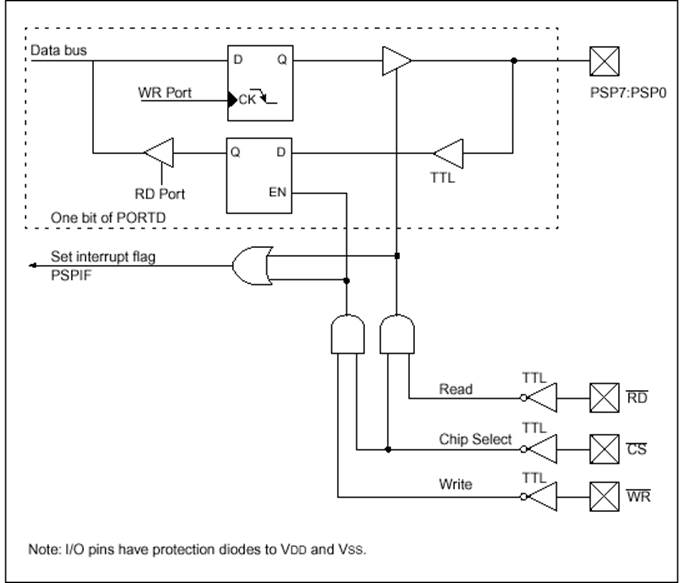

Деякі мікроконтролери містять відомий паралельний порт, мультипліцированний на один з портів вводу/виводу PORT працює як 8-розрядний паралельний порт (або порт мікропроцесора) коли біт PSPMODE установлений в '1' (до виводів підключені вхідні буфери ТТЛ).

У режимі веденого дані асинхронно читаються або записуються зовнішніми сигналами -RD й -WR відповідно.

За допомогою 8-розрядного веденого паралельного порту можна організувати інтерфейс зв'язку з мікропроцесором. Установка біта PSPMODE в '1' примусово наполягає виводи -RD, -WR й -CS як входи.

Примітка 1. У цей час ведений паралельний порт мультипліцирован тільки з PORTD PORTE. Порт мікропроцесора стає доступним тільки, коли біт PSPMODE установлений в '1'. У цьому режимі біти TRISE повинні бути встановлені в '1' (виводи настроєні як цифрові входи, АЦП відключений). Для PОRTD скасовується дія бітів TRISD.

Примітка 2. У режимі веденого паралельного порту до входів PORTD й PORTE підключені буфери ТТЛ. Біти керування PSP розташовані в регістрі TRISE.

Фактично існують два 8-розрядних регістри. Один регістр для прийому даних, іншої для передачі. Користувач записує 8-розрядні дані у вихідну засувку PORT, а читає дані із вхідної засувки (зверніть увагу, вихідна й вхідна засувка мають той самий адресу). У цьому режимі значення бітів регістра TRIS ігнорується, т до напрямком даних управляє зовнішній пристрій.

Структурна схема виводів PORTD й PORTE

(режим відомого паралельного порту).

Робота відомого паралельного порту

Запис в PSP відбувається, якщо виводи -CS й -WR мають низький рівень сигналу. Після переходу сигналу на виводі -CS або -WR у високий рівень (передній фронт сигналу) дані зберігаються у вхідній засувці на такті Q2. На такті Q4 установлюються в '1' біт IBF(TRISE<7>) і прапор переривань PSPIF/ Очищення біта IBF заблокована в додатковому циклі Тсу / Біт IBF може бути скинутий в '0' тільки читанням регістра PОRTD (командою MOVF, команди "читання - модифікації - запис" не повинні використатися). Біт переповнення IBOV(TRISE<5>) установлюється в '1'. якщо відбувся наступний запис в PSP, а попередній байт не був прочитаний

Читання з PSP відбувається, якщо виводи -CS й -RD мають низький рівень сигналу Негайно скидається в '0' біт OBF(TRISE<6>), що вказує, що PORTD прочитано зовнішньою шиною. Після переходу сигналу на виводі -CS або -RD у високий рівень (передній фронт сигналу) установлюється прапор переривання PSPIF на такті Q4 (тільки після такту Q2) указуючи, що читання завершене. Біт DBF залишається скинутим в '0" поки не будуть завантажені нові дані в PORTD програмою користувача.

Біт прапора повного вхідного буфера IBF установлюється в '1', якщо отримано нове слово, очікуване читання ЦПУ. Як тільки PORTD буде прочитаний, біт IBF апаратно скидається в '0'. Біт IBF відображає тільки стан прийомного буфера. Стан вихідного буфера відображає біт OBF. Якщо біт OBF=1, то в буфер записане слово, очікуване читання зовнішньою шиною. Як тільки вихідний буфер читається мікропроцесором, біт OBF апаратно скидається в '0'. Біт прапора переповнення вхідного буфера IBOV установлюється в '1' якщо мікропроцесор виконує запис нового слова, а попереднє слово не було прочитано ЦПУ (перше слово зберігається в буфері). Коли режим PSP виключений, біти IBF й OBF рівняються нулю а попередньо встановлений в '1' біт IBOV повинен бути скинутий програмно. Прапор переривання PSPIF установлюється в '1' по завершенню кожної операції читання або записи (скидається в '0' програмно). Дозволити/заборонити переривання від модуля PSP можна установкою/скиданням біта PSPIE.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.