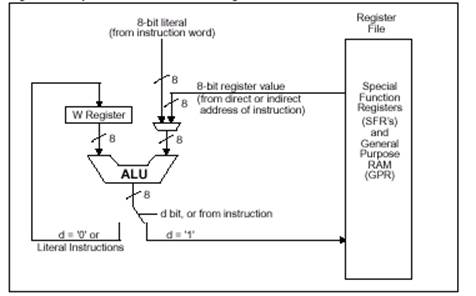

8 - розрядний АЛП може виконувати додавання, віднімання, порозрядний зрушення й логічні операції. Арифметичні операції виконуються за принципом доповнення до двох, якщо не зазначено інакше. У командах із двома операндами: перший операнд перебуває в одному регістрі W, другий - перебуває в регістрі пам'яті даних або константа. В командах з одним операндом є регістр W або регістр пам'яті даних.

Регістр W - не адресуємий 8-розрядний робочий регістр, що використається в операціях АЛП. Залежно від типу команди й результат команди АЛП може впливати на наступні прапори стану в регістрі STATUS: перенос (З), напівперенос (DC), прапор нульового результату (Z). Біти С и DC працюють як біти заема й десяткового заема при виконанні команд вирахування.

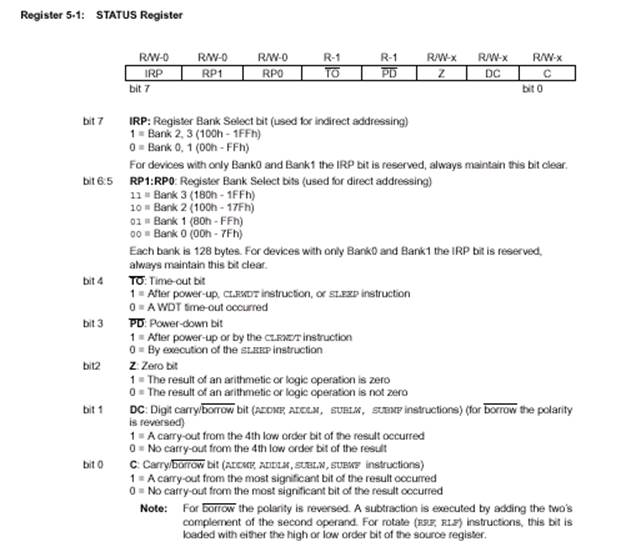

Регістр STATUS

У регістрі STATUS утримуються прапори стану АПП, прапор причини скидання мікроконтролера й біти керування банками пам'яті даних. Оскільки в регістрі STATUS присутні біти керування банками пам'яті необхідно, щоб він відображався у всіх банках пам'яті даних і мав однаковий зсув відносно початку банку.

Регістр STATUS може бути адресований будь-якою командою, як і будь-який інший регістр пам'яті даних. Якщо звертання до регістра STATUS виконується командою, що впливає на прапори Z, DC і 3 ту зміну цих трьох бітів командою заблоковано. Ці біти скидаються або встановлюються відповідно до логіки ядра мікроконтролера. Команди зміни регістра STATUS також не впливають на біти -ТЕ й -PD Тому результат виконання команди з регістром STATUS може відрізнятися від очікуваного. Наприклад, команда CLRF STATUS скине три старших біти й установить біт Z (стан регістра STATUS після виконання команди 000uu1uu, де u - не змінюваний біт).

При зміні бітів регістра STATUS рекомендується використати команди, що не впливають на прапори АЛП (SWAPF, МOVWF, BCF й BSF)

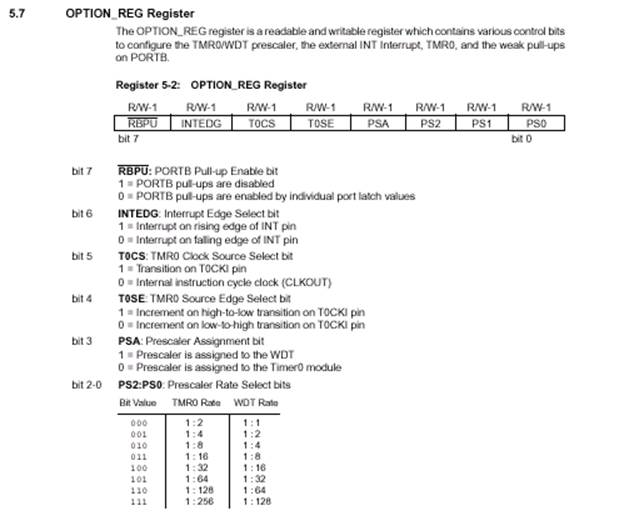

Регістр ОРTION

Регістр ОРTION_REG доступний для читання й запису, включає біти керування:

• Попереднім дільником TMRO/WDT.

• Активним фронтом зовнішнього переривання RBO/INT;

• резисторами, Що Підтягують, на входах PORTS.

Введення

У цьому розділі - "Організація пам'яті", описується два незалежних блоки пам'яті пам'ять програм і пам'ять даних. Кожен блок має власну шину дані й шину адреси, дозволяючи організувати одночасний доступ до обох типів пам'яті протягом одного машинного циклу.

Пам'ять даних складається з регістрів загального (GPR) і спеціального (SFR) призначення.

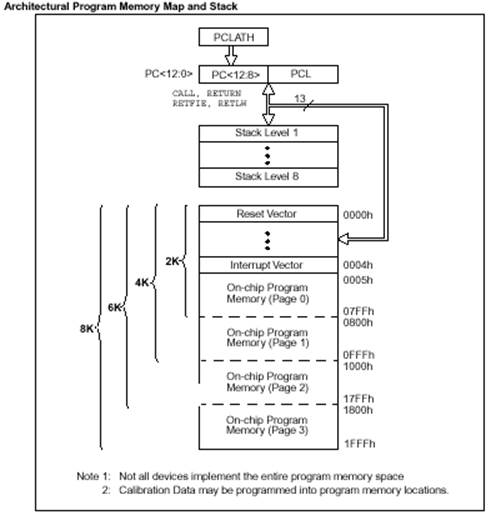

Організація пам'яті програм

Мікроконтролери середнього сімейства мають 13-розрядний лічильник команд здатний адресувати 8K х 14 слів пам'яті програм, і 14-розрядну шину дані пам'яті програм. Всі команди мікроконтролера складаються з 14-розрядного слова, тому мікроконтролер з обсягом пам'яті програм 8К х 14 може містити 8К команд. Це дозволяє легко визначити достатність обсягу пам'яті програм для бажаного додатка.

Вся пам'ять програм розділена на 4 сторінки по 2Кслов кожна (0000h-07FFh 0800h-0FFFh. 1000h-17FFh, 1800h-1FFFh). На малюнку показана карта пам'яті програм й 8-рівневий апаратний стек. Залежно від типу мікроконтролера, тільки деяка частина доступної пам'яті програм реалізована апаратно. Для переходу між сторінками пам'яті програм необхідно змінити старші біти регістра лічильника команд PC, записом у регістр спеціального призначення PCLATH (старший байт лічильника команд). Змінивши значення регістра PCLATH і виконавши команду розгалуження, лічильник команд PC перетне границю сторінки пам'яті програм без додаткового втручання користувача.

Для мікроконтролерів, що мають пам'ять програм менше 8Кслов. звертання до пам'яті програм вище фактично реалізованого значення приведе до циклічної адресації. Наприклад, у мікроконтролері з пам'яттю програм 4Кслов і спробі переходу за адресою 17FFh перехід буде виконаний за адресою 07FFh. У мікроконтролерах з пам'яттю програм 2Кслов керування сторінками пам'яті не потрібно

Карта пам'яті програм й 8 - розрядний апаратний стек.

Вектор скидання

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.